# AMS Timing Closure with Coside

Using timing-aware models and static analysis techniques

Guillermo Conde Infineon Technologies Austria 04.11.2020

- 1 Introduction

- Timing in Synchronous Digital Systems

- Timing in AMS Systems

- 4 SystemC timing-aware models

- 5 Coming next ...

- Introduction

- 2 Timing in Synchronous Digital Systems

- Timing in AMS Systems

- SystemC timing-aware models

- Coming next ...

#### Introduction

- Timing closure is the process by which a logic design (sequential + combinatorial gates) is modified to meet its timing requirements.

- Semi-custom logic designs meeting timing closure via Static Timing Analysis (STA).

- Timing requirements are translated into static timing constraints to the EDA tool.

- Models including accurate timing characterization

- > Lack of systematic timing closure in AMS designs.

- No timing requirements in place.

- Models do not include any timing characterization.

- Timing issues detected very late in development

#### Goals

- To extract timing requirements from full custom designs

- Yes the timing of standard cells at System C level

- Delays

- Timing constraints

- To perform a simulation-based timing analysis in order to fullfill all timing requirements.

- Voltimate goal: To develop a static timing analysis tool to be applied in AMS designs in early development stages.

- 1 Introduction

- Timing in Synchronous Digital Systems

- Timing in AMS Systems

- 4 SystemC timing-aware models

- 5 Coming next ...

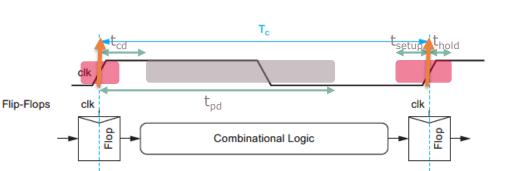

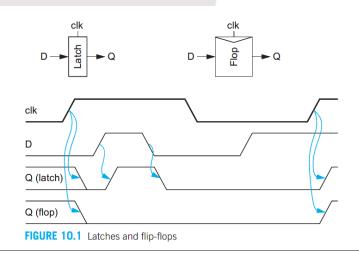

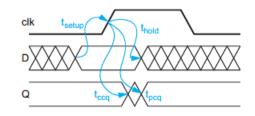

# Timing basics in digital systems

Most common sequencing elements are latches and flip-flops

Basic timing contraints and delays

2020-11-04

- Worst case scenario known including PVT

- Systematic method to guarantee proper timing (STA)

- Systems insensitive to PVT variations once timing is guaranteed

Digital flow rules: Synchronous systems based on FFs and constant clock period

**Infineon Proprietary**

Source: CMOS VLSI Design, Neil H.E Weste

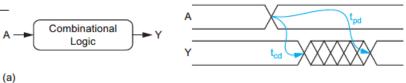

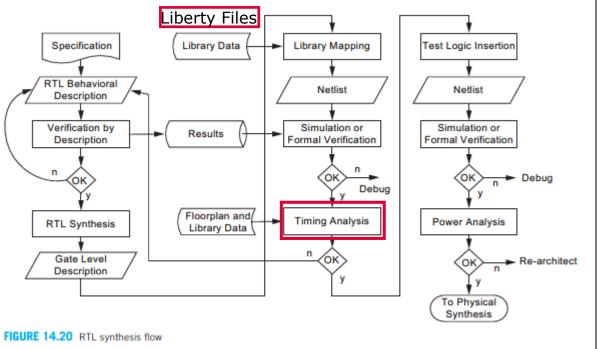

## Semi-custom design flow

2020-11-04

- STA evaluates automatically all timing paths

- Intrinsic gate delay derived from the library

- Loads are either estimated statiscally or derived from the floorplanning.

Timing information available in the early phases of development

Source: CMOS VLSI Design, Neil H.E Weste

**Infineon Proprietary**

- 1 Introduction

- Timing in Synchronous Digital Systems

- Timing in AMS Systems

- 4 SystemC timing-aware models

- 5 Coming next ...

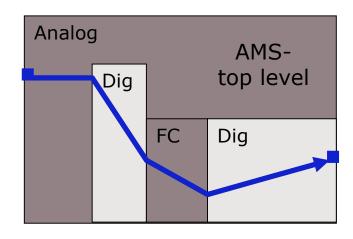

### AMS design components

- Semi-custom logic (digital part) composed of:

- Logic gates

- Sequential gates

- Flip-flops

- AMS designs composed of:

- Analog part

- Full-custom logic: Timing provided in Liberty files

- Analog blocks: Timing characterization has to be calculated

- Digital part: Timing closure determined by STA tools

Full-custom logic (in the analog design flow) composed of

- Logic gates

- Sequential gates

- Flip-flops

- Latches

- Special cells

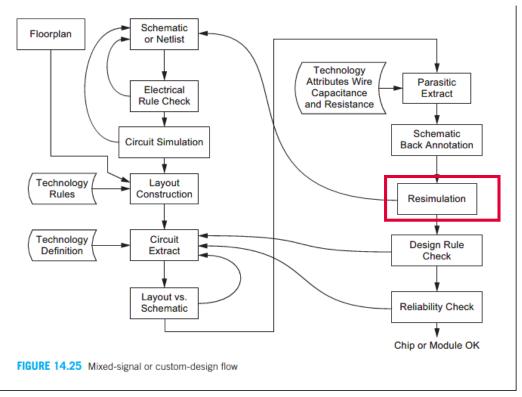

## Full-custom design flow

- Extracted simulation at system level late in the development phase

- Simulation is required

- no timing analysis tools available

- Potential failing scenarios have to be identified in advanced

Source: CMOS VLSI Design, Neil H.E Weste

- 1 Introduction

- Timing in Synchronous Digital Systems

- Timing in AMS Systems

- 4 SystemC timing-aware models

- 5 Coming next ...

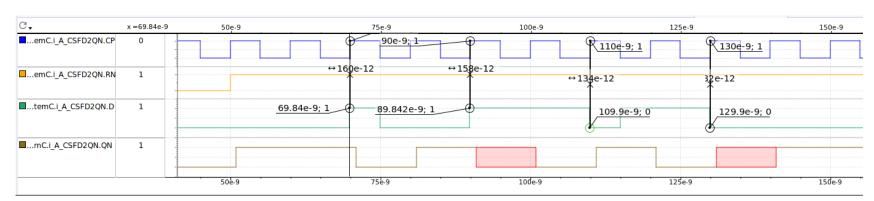

## Timing-aware models

- System C models with 4-value data types

- Delay included

- Time stamps taken at every event

- Automatic checks on

- Setup and hold time

- Reset recovery and removal

- Minimum Pulse Width

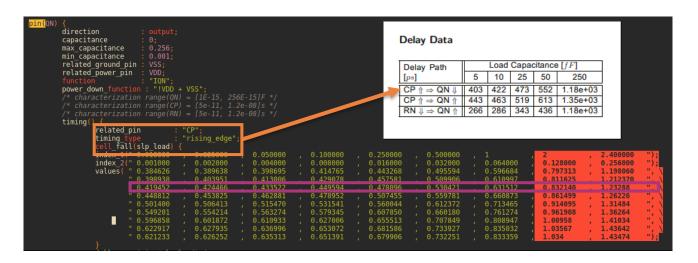

| Delay Path                                       | Load Capacitance [fF] |     |     |     |          |

|--------------------------------------------------|-----------------------|-----|-----|-----|----------|

| [ps]                                             | 5                     | 10  | 25  | 50  | 250      |

| CP ↑ ⇒ QN ↓                                      | 403                   | 422 | 473 | 552 | 1.18e+03 |

| $CP \uparrow \Rightarrow QN \uparrow$            | 443                   | 463 | 519 | 613 | 1.35e+03 |

| $RN \downarrow \Rightarrow QN \uparrow \uparrow$ | 266                   | 286 | 343 | 436 | 1.18e+03 |

|                    | Constraint [ps] |  |  |

|--------------------|-----------------|--|--|

| Check              | typ             |  |  |

| D                  | 133             |  |  |

| D                  | 14.9            |  |  |

| D ↑ setup CP ↑     | 159             |  |  |

| D ↑ hold CP ↑      | 24.2            |  |  |

| RN ↑ recovery CP ↑ | -261            |  |  |

| RN ↑ removal CP ↑  | 263             |  |  |

| MPW    | value [ps] |

|--------|------------|

| CP (L) | 173        |

| CP (H) | 156        |

| RN (L) | 274        |

- Limitations

- Manual set of timing parameters

- Only valid for one corner

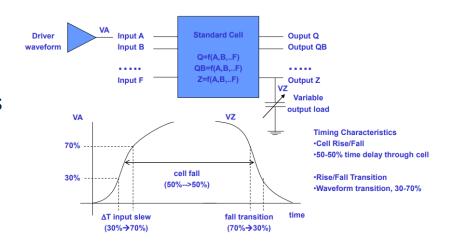

#### Liberty Files

- Open Source ASCII format to specify:

- PVT Characterization

- Relating Input and Output chracteristics

- Timing

- Power

- Noise

- Cell delays/constraints depending on:

- Input slew

- Output load

Joseph A. Elias, Ph.D, University of Kentucky, Adjunct Professor, ECE Dept; Cypress Semiconductor MTS

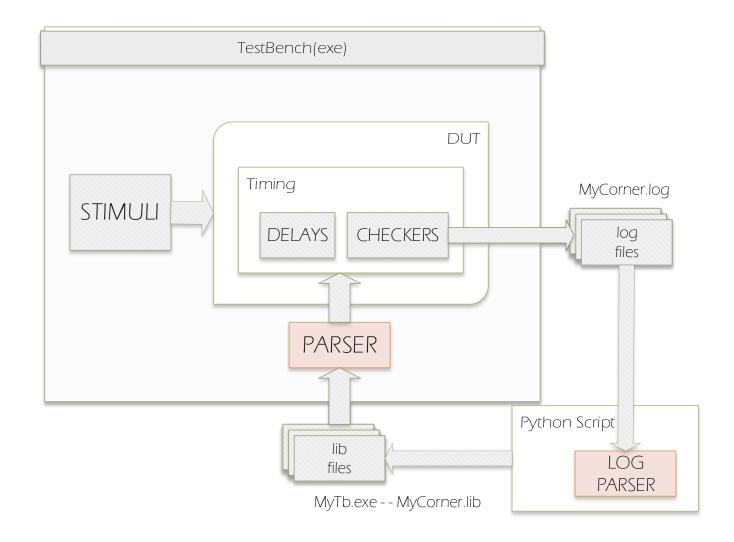

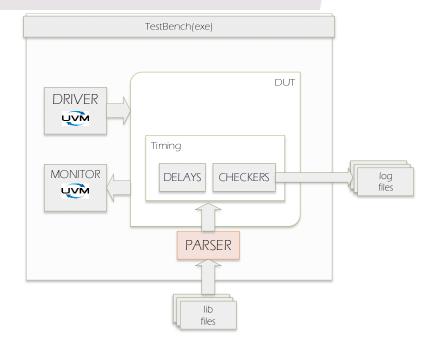

# **AMS Timing Closure Automation**

- 1 Introduction

- Timing in Synchronous Digital Systems

- Timing in AMS Systems

- 4 SystemC timing-aware models

- 5 Coming next ...

## Coming next...

- Limited verification environment

- No input constraints

- No system-level checks

- Simulation-based environment

- Formal static analysis

- Automatic calculation of timing parameters based on output load and input slew

- Formal Timing analysis based on system properties:

- Cell delay

- Standard-cell timing constraints

Part of your life. Part of tomorrow.