Zynq-7000 arm based HIL

THE ANALOG AND DIGITAL SYSTEM LEVEL COMPANY

#### Outline

- Introduction/Motivation

- Flow

- Example platform ZedBoard

- COSIDE integration

- Conclusion/ Outlook

#### Introduction

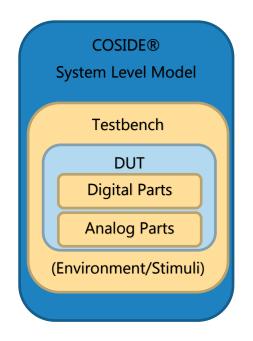

- System level design

- SystemC, SystemC AMS, UVM, VHDL/Verilog

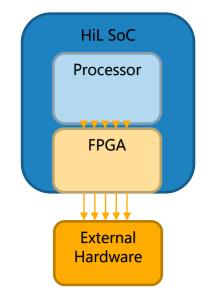

- Hardware in the Loop HiL

- Processor, FPGA, connectivity to External Hardware

Used to test and develop complex real-time embedded systems

#### Motivation

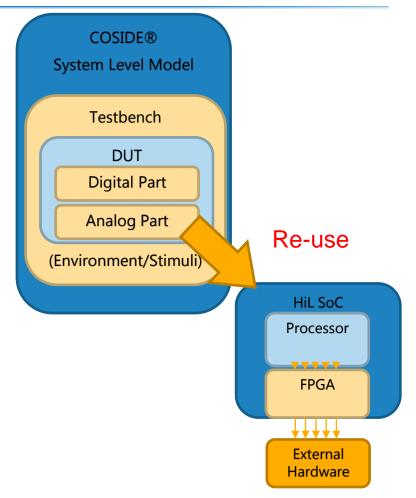

- Re-use / simulate COSIDE<sup>®</sup> system models/testbenches in a lab environment

- Re-use as much as possible from the COSIDE system level model:

- **Stimuli** no need to re-write, for real hardware lab validation

- modeled Environment of complex systems (e.g. processor with firmware)

- Analog Part before analog test chips are available, very low hardware costs

- Digital Part as FPGA prototype

- Substitute parts of the model by real hardware / FPGA (sign-off or simulation speed-up)

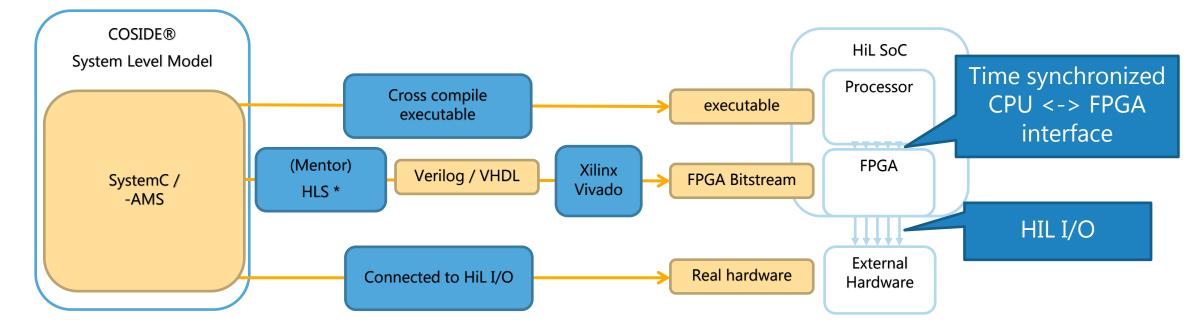

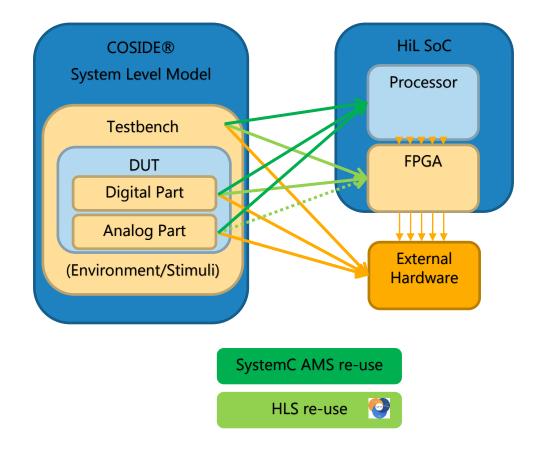

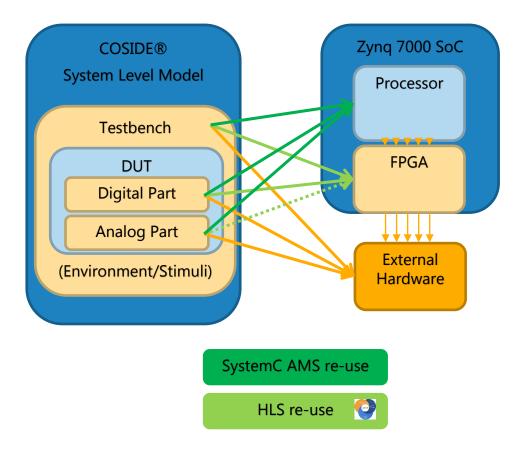

Flow – From COSIDE<sup>®</sup> System Level Model towards Hardware in the Loop - Example Partitioning

- SystemC / -AMS model has to be mapped to either processor, FPGA or into external hardware

- Steps from the System Level Model towards the HiL simulation:

\*if Verilog/VHDL implementation is available this can be skipped

#### Conclusion

- SystemC / AMS parts are re-used on the processor

- HLS can be used to convert SystemC into synthesizable Verilog/VHDL (even analog parts can be modeled as digital filters)

- Constraints for this partitioning: processor speed, FPGA size, I/O-count, CPU<->FPGA interface (timing and bandwidth)

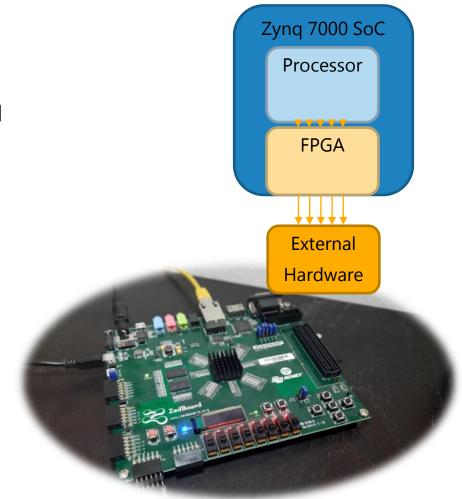

ZedBoard - Example of the Zynq-7000 family

- ZedBoard System on Chip (SoC)

- 2x A9 ARM cores 666 MHz and 512 MB DDR3 RAM

- Neon floating point unit

- Ethernet and SD-Card

- Programable logic with 85k logic cells (FPGA)

- Fast interconnect between processor and FPGA

- 100+ I/O's to external hardware including FMC, buttons, LEDs ...

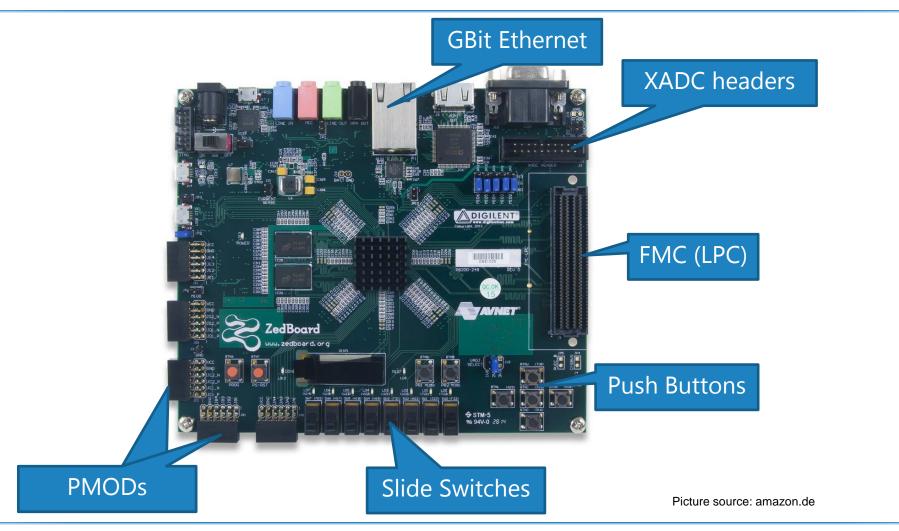

ZedBoard - I/O

COSIDE integration - ZedBoard Pack

- COSEDA provides a ZedBoard pack

- Real-time patched Linux system

- GCC cross compiler with hard float neon support

- SystemC with ARMv7 Quick Thread patch and SystemC AMS

- Full COSIDE<sup>®</sup> library stack 800+ elements cross compiled for ARMv7

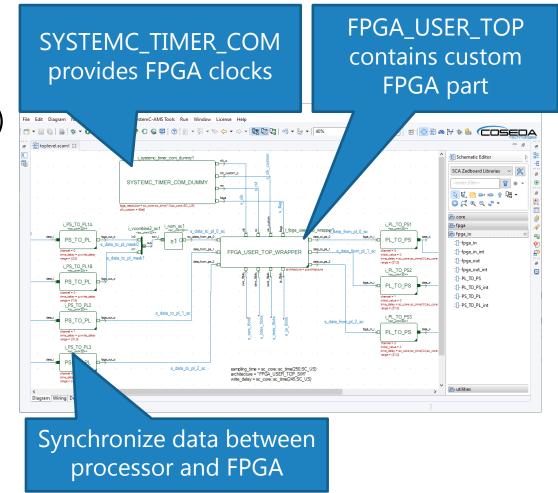

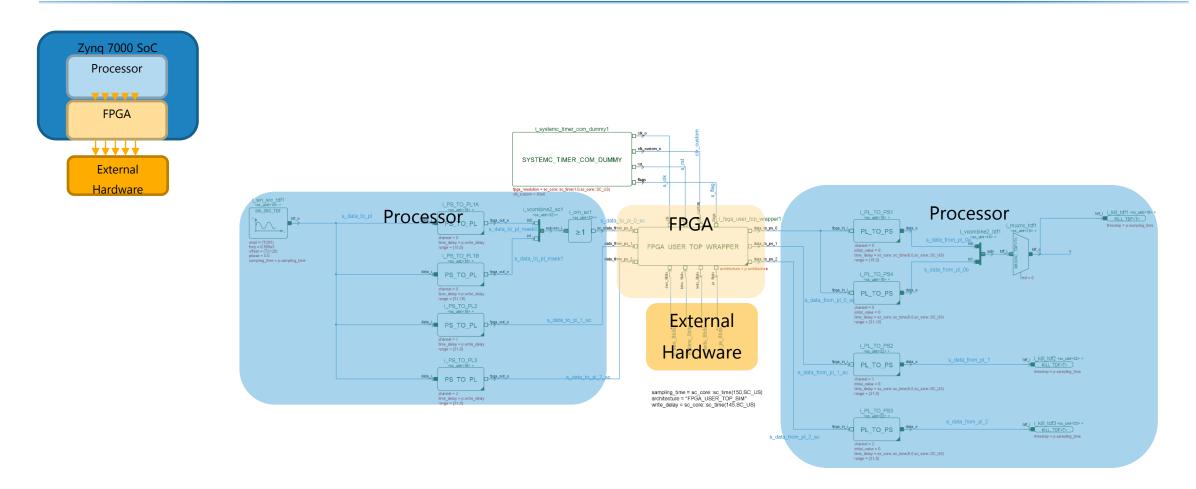

**COSIDE integration - schematic**

- Graphical partitioning within COSIDE<sup>®</sup>

- Sync modules couple between CPU(PS) and FPGA(PL)

- For data and time synchronization

- FPGA\_USER\_TOP contains the part which will be in the FPGA bitstream

- High level synthesis can be used

- SYSTEMC\_TIMER\_COM\_DUMMY

- Provides FPGA clocks to the SystemC model

# COSEDA® Hardware in the Loop Simulation

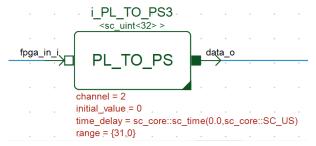

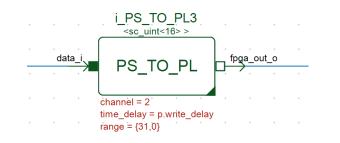

COSIDE integration - CPU (PS) and FPGA(PL) Interface (sync modules)

- Highly accurate time synchronization mechanism between the processing system PS (CPU) and programable logic PL (FPGA)

- PL\_TO\_PS uses a FPGA clock to capture data at a precise point in time

- PS\_TO\_PL uses the same clock to write the data at a precise points in time

- Interface consists of 8 channels each 32 bit wide

- Both direction can handle template types castable to a 32bit integer

- The range attribute allows the combination of smaller signals into an 32bit integer

#### **COSIDE** integration - Partitioning

**COSIDE integration - Vivado Tool integration**

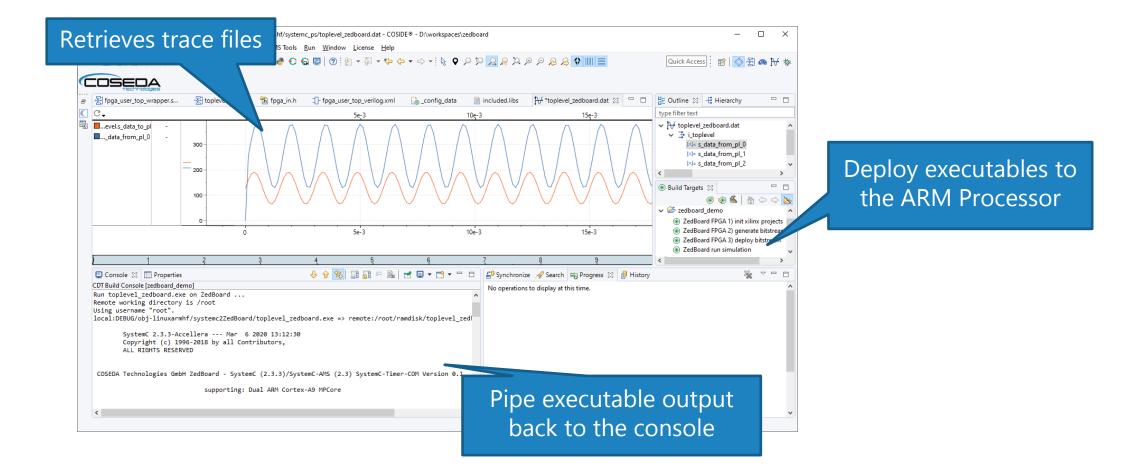

- COSIDE manages Xilinx flow including the bitstream generation via build targets

- COSIDE manages the Xilinx environment

- generates Block Level IP of the users

Verilog part

- ZedBoard FPGA 1) init xilinx projects

ZedBoard FPGA 2) generate bitstream

ZedBoard FPGA 3) deploy bitstream

ZedBoard run simulation

- Includes a coupling IP for timing and data synchronization

- Manages the constraints file to describe interface to external hardware

- COSIDE allows bitstream generation and live deployment to the ZedBoard

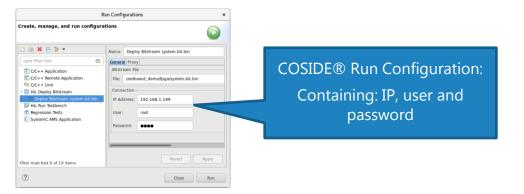

#### **COSIDE** integration - simulation control frontend

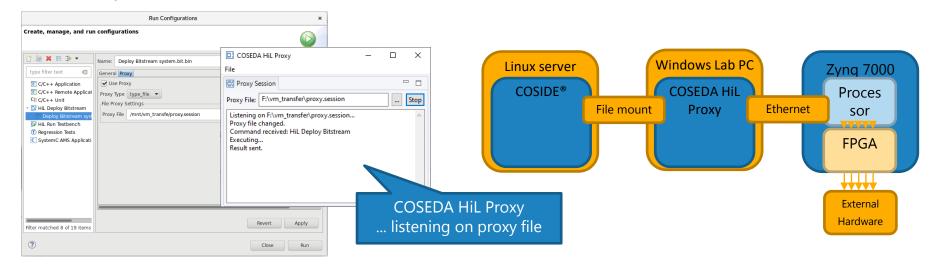

#### **COSIDE integration - ZedBoard communication**

Normal communication via Ethernet

• The COSEDA Proxy allows to control the ZedBoard from a Linux server via a shared file

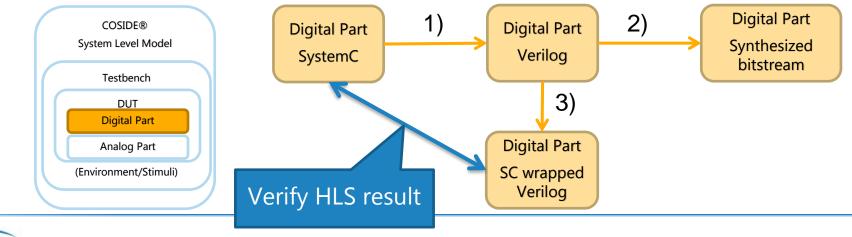

COSIDE integration - Extension: Verilog Co-simulation & HLS

- 1) High level synthesis HLS to replace selected SystemC- by (System-)Verilog-(AMS) modules (e.g. Mentor Catapult)

- 2) Synthesized Verilog to FPGA bitstream

- 3) Simulator coupling to wrap Verilog into the SystemC simulation (e.g. Cadence Incisive, Xilinx xsim, Verilator)

#### Conclusion

- All models parts are mapped into either CPU, FPGA or into external hardware

- Partitioning is done on schematic level

- COSIDE supports Mentor HLS and Vivado bitstream generation

- COSIDE provides as Addon ZedBoard pack with cross-compiler, sync modules and libraries

- HiL simulation is controlled from within COSIDE<sup>®</sup>

#### Outlook

### Outlook

- Further flow improvements ... adoptions towards other boards

- Analog synthesis into FPGA as digital filters models

- Looking forward for challenges and new projects in this area

#### Thank you for Your Attention

#### Paul Ehrlich

- Senior Application Engineer

- paul.ehrlich@coseda-tech.com

- **+49 351 321490-56**

#### **Thomas Hartung**

- Marketing & Sales

- thomas.hartung@coseda-tech.com

- +49 351 321490-31

COSEDA Technologies GmbH Koenigsbruecker Str. 124 01099 Dresden Germany

www.coseda-tech.com