## Mastering Unexpected Situations Safely

SensePlanAct

Chassis & Safety | Vehicle Dynamics

#### **System Evaluation of UVM-SystemC** Coside Usergroup Meeting 18.10.2016

www.continental-corporation.com

**Division Chassis & Safety**

| 1 | Motivation                    |

|---|-------------------------------|

| 2 | Introduction into UVM-SystemC |

| 3 | Module Level Verification     |

| 4 | System Level Verification     |

| 5 | Results                       |

| 6 | Outlook                       |

#### SystemC IP Validation before UVM-SystemC

#### > Module Level

| enter_test_mode_enter_test_mode_<br>tmout_0_out_s_tmout_out_s<br>tmout_1_out_s_tmout_out_s<br>bypass_wd0_s_bypass_wd0_s | i_testmode_ts1 | tmgut0_pwm_tmout0_pwm_s<br>tmgut1_pwm_tmout1_pwm_s<br>tmgut0_spc_tmout0_spc_s<br>tmgut1_spc_tmout1_spc_s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tmout0 <u>pwm s</u> tmout0pwm<br>tmout1 <u>pwm s</u> tmout1pwm<br>tmout0 <u>spc s</u> tmout0 <u>pc</u><br>tmout1 <u>spc s</u> tmout0 <u>spc</u>                                                                          | i_testmode1 | reter test moderiter test mode_s<br>tmout0_out tmout0_out_s<br>mout1_out tmout1_out_s<br>bygass_wd0_bypass_wd0_s |

|-------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------|

| bypas <u>s wd1 s bypass_wd1-s</u><br>t <u>mana2 s tmana2-y</u>                                                          |                | tmouto_can_tmouto_can_s<br>tmouto_can_tmouto_can_s<br>tmouto_can_tmouto_can_s<br>tmouto_can_tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s<br>tmouto_can_s                                                                                                                                | tmout <u>0 can s tmout0 can</u><br>tmout <u>1 can s tmout0 can</u><br>tmout <u>0 rdm s tmout0 rdm</u><br>tmout <u>1 rdm s tmout1 rdm</u><br>tmout <u>0 logic s tmout0 logic</u>                                          |             | bygass_wd1_bypass_wd1_s<br>tmana2tmana2_s                                                                        |

| Describe test<br>stimuli in a                                                                                           | TESTMODE_TS    | moutlegic tmoutlegics<br>moutlegic tmoutlegics<br>moutlegic tmoutlegics<br>moutlegic tmoutlegics<br>moutlegic tmoutlegics<br>moutlegic tmoutlegics<br>moutlegic tmoutlegics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tmout1 logic s tmout1 logic<br>tmout0 slp s tmout0 slp<br>tmout1 slp s tmout1 slp<br>tmout1 mpo s tmout1 mpo<br>tmout1 mpo s tmout1 mpo<br>tmout1 mpo s tmout1 mpo<br>tmout1 mpo s tmout1 mpo<br>tmout1 mpo s tmout1 mpo | TESTMODE    | Good for module<br>level. However, no                                                                            |

| SystemC mirror<br>module. Either<br>schematic or code.                                                                  |                | mouti-pc tmouti pc_s<br>poin poins<br>psin psinx s<br>psinx | tmout1_rpc_s_tmout1_rpc<br>por_n_spor_n_<br>psi1rx_spsi2rx_s<br>tpm_tmana2_s_tpm_tmana2_<br>spc_tmana2_s_spc_tmana2_<br>test_mode_slave_test_mode_slave_s                                                                |             | reuse at system<br>level. Mainly visual<br>inspection.                                                           |

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

#### SystemC Validation before UVM-SystemC

🛈 ntinental 🏂

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

#### **Requirements to next testbench generation**

- Standardized format for stimuli and result checks

- > No secret waveform generators

- > Can run in regression

- > Module level tests (partly) reusable at toplevel

| 1 | Motivation                    |

|---|-------------------------------|

| 2 | Introduction into UVM-SystemC |

| 3 | Module Level Verification     |

| 4 | System Level Verification     |

| 5 | Results                       |

| 6 | Outlook                       |

#### What is UVM?

- Universal Verification Methodology to create modular, scalable, configurable and reusable test benches based on verification components with standardized interfaces

- > Class library with features dedicated to verification, e.g.,

- phasing

- component overriding (factory)

- configuration

- scoreboarding

- > reporting

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

#### Main concepts in UVM

- > Clear separation of test stimuli and test bench

- So stimuli can be developed and reused independently

- > Test bench abstraction levels

- Test bench components communicate in TLM

- > Non-intrusive test bench configuration and customization

- > configuration and resource database

- Factory design pattern

- > Well defined execution (phases) and synchronization (objections) process

- > Reusable verification components

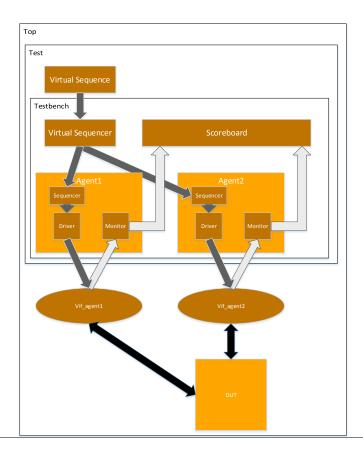

#### **General UVM setup**

Ontinental 🏂

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

#### **UVM-SystemC**

- > Developed in the EU 7th framework programme Verdí (2011 2014)

- > Continental participated in Verdi

- > Donated to accelera public preview release available since December 2015

- > At Continental currently work is ongoing to put UVM-SystemC into industrial use.

| 1 Motivation                    |  |

|---------------------------------|--|

| 2 Introduction into UVM-SystemC |  |

| 3 Module Level Verification     |  |

| 4 System Level Verification     |  |

| 5 Results                       |  |

| 6 Outlook                       |  |

|                                 |  |

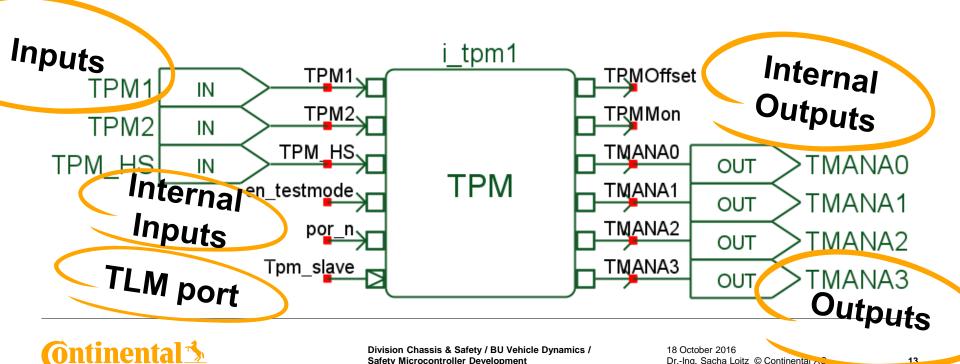

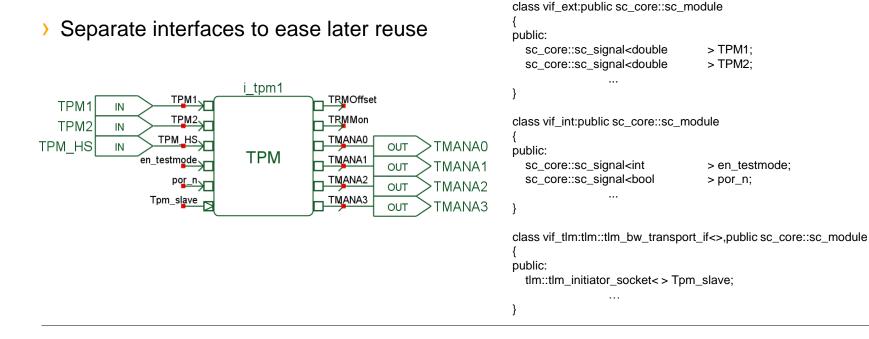

#### **Detailed view on a Module**

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

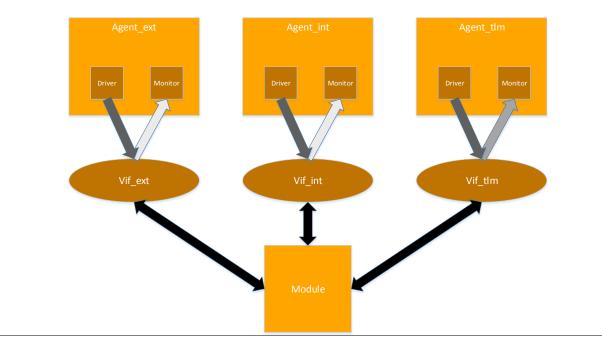

#### Module level test setup with UVM-SystemC

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

#### **Agents for Module Level Test Setup**

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

18 October 2016 Dr.-Ing. Sacha Loitz © Continental AG

16

| 1 | Motivation                    |

|---|-------------------------------|

| 2 | Introduction into UVM-SystemC |

| 3 | Module Level Verification     |

| 4 | System Level Verification     |

| 5 | Results                       |

| 6 | Outlook                       |

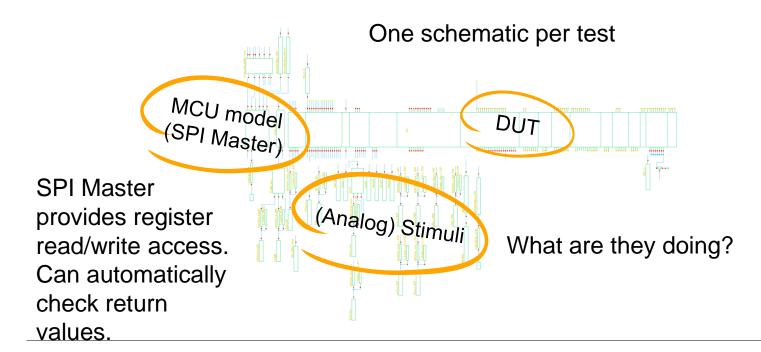

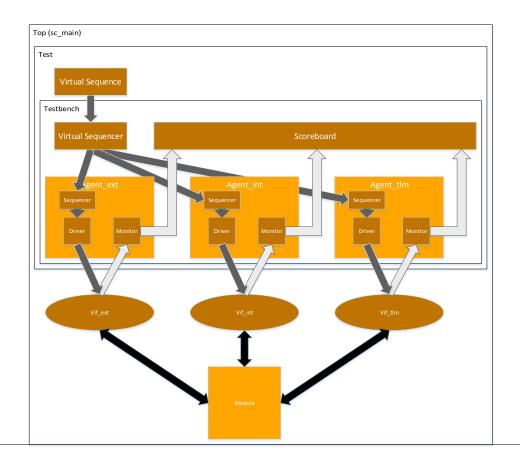

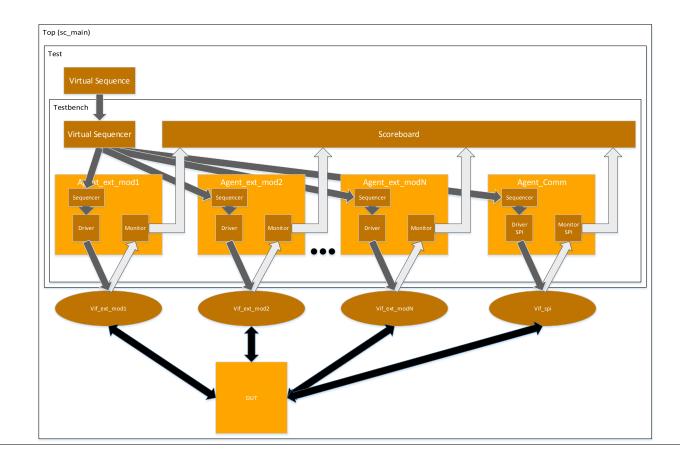

### **Going up to System-Level**

- > External pins also exist at system level

- Reuse Agent\_ext

- > Internal pins are not accessible at system level

- > Outputs are not directly observable

- > Inputs need to be provided by other modules

- > TLM bus not accessible at system level

- > Access handled by e.g. SPI interface

- Agent on communication interface shall be able to process the same sequences as Agent\_tlm

18 October 2016 Dr.-Ing. Sacha Loitz © Continental AG

19

| 1 | Motivation                    |

|---|-------------------------------|

| 2 | Introduction into UVM-SystemC |

| 3 | Module Level Verification     |

| 4 | System Level Verification     |

| 5 | Results                       |

| 6 | Outlook                       |

#### **Results**

- > Better test coverage

- > No need of extra stimulus modules or test benches to test some special cases

- > No need of dedicated test stimulus modules

- > Still need agents

- > Reuse: agents, interfaces, monitors from module level to system level test setup

- > Little extra effort in creating system level test setup

- Module level test sequences abstracting some bit transactions can be reused at system level

#### **Results**

- > Structured verification environment

- > Easy for new/other teammates to learn & contribute

- > Configurability

- > Analog pins can be easily observed

- > Instead of manual waveform analysis

#### Coside UVM Generator

> In a first trial we manually created our UVM test bench.

- > High manual effort 1-2 PM

- > Most of the time goes in generation and debug of framework

- > Recreation with alpha version of UVM Generator

- > Framework generation within one day

- > Test setup within one week

| 1 | Motivation                    |

|---|-------------------------------|

| 2 | Introduction into UVM-SystemC |

| 3 | Module Level Verification     |

| 4 | System Level Verification     |

| 5 | Results                       |

| 6 | Outlook                       |

#### **Future Work**

- Generation of possible top level sequences

- From module level sequences we can directly reuse external and TLM part of the sequence

- > What about internal signals?

- > Idea:

- > Detemine module level sequences driving this signal as expected.

- > Combine sequences to system level sequences.

Thank you for your attention!

# **ASIC** solutions for Vehicle Dynamics

Division Chassis & Safety / BU Vehicle Dynamics / Safety Microcontroller Development Public

# Safe and Dynamic Driving towards Vision Zero

**Ontinental**\*

#### Sense**PlanAct** Chassis & Safety