### Green**Socs** Purveyor of fine Open Source Virtual Platform Technology and Services Since 2005

Green**Socs** Virtual Platforms let you **imagine**, design, **develop** and **test** your embedded application as a whole; **size your hardware** to reflect the **needs of your software**; build your software and hardware together; debug your software and **verify** your hardware **efficiently**.

> Feb 2016 Mark Burton

#### Green**Socs**: Integrated Virtual Platforms

- GreenSocs® is the industrial leader in integrating different Virtual Platform solutions

- Dr Mark Burton is the founder of GreenSocs. Mark has worked for ARM managing their modeling group. He was the chair of the OSCI TLM WG and the OCP-IP SLD WG.

- GreenSocs provided technology behind the TLM-2.0 standard, and the CCI standard. We continue to be at the heart of SystemC development.

- GreenSocs is a contributor to QEMU, providing technology to support multi-thread and reverse execution.

- GreenSocs has been in business (incorporated in UK and France), and profitable, since 2005, including within its client base large multi-nationals.

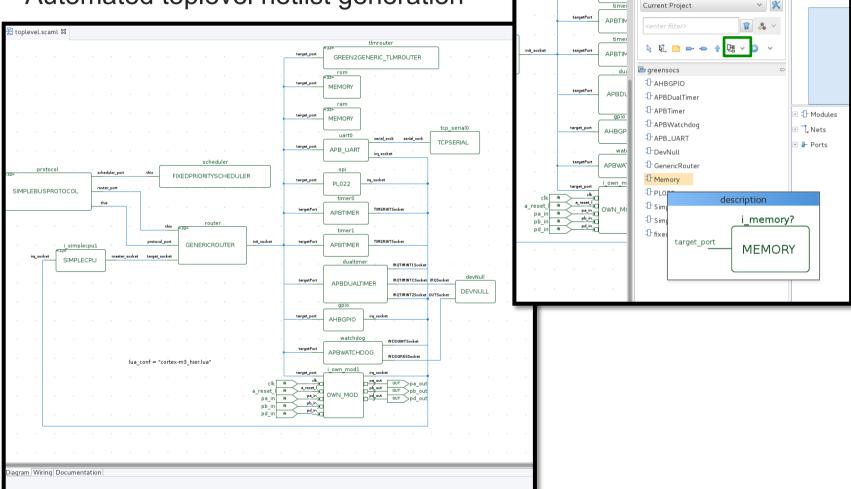

#### COSIDE: Cortex M3 Toplevel

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        | temC           | -AMS - gree | enarm, ub/co           | Jievei.sca       | imi – CO   | SIDE    | - /nom | e/enru | n/won | kspace | 5/ d1 111 |  |        |        |    |       |                           |            |       |    |

|-----|------|---------|-----------|--------|---------|---------|-----------|-------------------|----------|---------|-------|--------------|---------|-------|---------|----------|--------|----------------|-------------|------------------------|------------------|------------|---------|--------|--------|-------|--------|-----------|--|--------|--------|----|-------|---------------------------|------------|-------|----|

| dit | Diag | iram    | Nav       | vigate | e Sea   | arch    |           | ct S <sup>.</sup> |          |         |       |              |         |       |         | ense     |        | <u> </u>       | / ⇔ ∨   [   |                        | ₽ ~              | 11%        |         | ~      |        |       |        |           |  | Quick  | Access |    | e   🛙 | > 몸 ∞ ⊮                   | * 🕒        |       |    |

|     |      | [0      | <u>10</u> | . se   |         |         |           |                   | ~        |         | 6     | <u>- </u> ън |         | Ū     | 1 200   | . Au     | · •    | ~ .            | - 10        |                        | 40 I U           | 41/0       |         |        |        |       |        |           |  | Grutek | Acces  | 11 | 6   N | s 53 👐 10.                | .14. [2004 |       | те |

| top | olev | el.sci  | aml S     | 3      |         |         |           |                   |          |         |       |              |         |       |         |          |        |                |             | timrouter              |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       | -  |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | target | port           | <32>        |                        |                  |            |         |        |        |       |        |           |  |        |        |    | 물     | Schematic Edi             | tor        |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        | -              |             | ENERIC_TLM             | ROUTER           |            |         |        |        |       |        |           |  |        |        |    |       | Current Project           |            | ~     |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | target |                | *32>        |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       | _  |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                | MEMORY      |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       | <enter filter=""></enter> |            | 1     | 8  |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        | ŕ              | ram         |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       | k K. 🖿 🗖                  | • • •      | 면 🗸 🖸 | ,  |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | tärget | _port          | MEMORY      |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                | uart0       |                        | serial_sock      |            | serial0 | ٦.     |        |       |        |           |  |        |        |    |       | greensocs<br>greensocs_ba | ckand      |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | target | port           | APB_UART    | ing_socket             |                  | - ICPS     | ERIAL   |        |        |       |        |           |  |        |        |    |       | lib                       | ckenu      |       |    |

|     |      | prot    | ocol      |        |         |         |           |                   |          |         |       | sch          | heduler |       |         | <u> </u> |        | l              | -spi -      |                        |                  | ]          |         |        |        |       |        |           |  |        |        |    | 11    |                           |            |       | Ī  |

|     |      | proc    | 0001      |        |         | schedul | er_port   | -                 | this     | FD      | XEDP  | RIORIT       | rysch   | EDULE | R       |          | target | _port          | PL022       | inq_sock et            |                  | [ ```      |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

| Μ   | PLE  | BUSF    | PROT      | DCOL   |         | router_ | oort      |                   |          |         |       |              |         |       |         |          |        | ·              | timer0      |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         | this    |           |                   |          |         |       |              |         |       |         |          | targe  | tPort ·        | APBTIMER    | TIMERINTSoc            | ket .            |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          | this    | _     | ro           | outer   |       |         |          |        | . (            |             |                        |                  | Ι          |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         | ≪32≻  |              |         |       |         |          | targe  |                | timerl      | TIMERINTSoc            | h-1              |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         | (* 32     | i_simp | plecpu  |         | L         |                   | protocol |         | GE    | NERIC        | ROUT    | ER    | init_so | cket -   | targe  | tron           | APBTIMER    | TIMERINTSOC            | :et              |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     | Inc  | _socket | τ         | SIMPL  | LECPU   |         | master_so |                   | target_s | iocket  |       |              |         |       | J.      |          |        |                | , dualtim   | er . IRG               | QTIMINT1 Sock et |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | targe  | tPort_         | APBDUALI    |                        | TIMINTCSocket    | IRQSock et | de      | vNull  |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                |             |                        | QTIMINT2Socket   | OUTSocket  | DEV     | NULL   |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        | . (            | gpio        | <br>]                  |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | target | _port          | AHBGPIO     | ing_sock et            |                  | •          |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                | . watchdo   | g . wria               | GINTSocket       |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          | targe  | tPort          | APBWATCHI   | 006                    | GRESSocket       |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           | lua_co            | nf = "o  | cortex- | m3_hi | ier lua'     |         |       |         |          |        | ·              | i_own_mod1  |                        | INESSOCKET       | · ·        |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         | clk      | target | clk            |             | pa_out OU<br>pb_out OU |                  | •          |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       | a_re    | set_     |        | eset_l         | OWN_MOD     | pb_out OU<br>pd_out OU |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       | р       | b_in     |        | pb_in<br>pd_in |             |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   | · .      | · ·     |       |              |         |       | p       | <u></u>  |        |                |             |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                |             |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

|     |      |         |           |        |         |         |           |                   |          |         |       |              |         |       |         |          |        |                |             |                        |                  |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

| -   |      |         |           |        | entatio |         |           |                   |          |         |       |              |         |       |         |          |        |                |             |                        | _                |            |         |        |        |       |        |           |  |        |        |    |       |                           |            |       |    |

Green**Socs**

#### COSIDE: Cortex M3 GreenSocs Modules Library

COSIDE provides symbols for the GreenSOCs library models

GreenSocs

🔁 Schematic Editor

target\_port

PL022

- Allows graphical system assembly

- Automated toplevel netlist generation

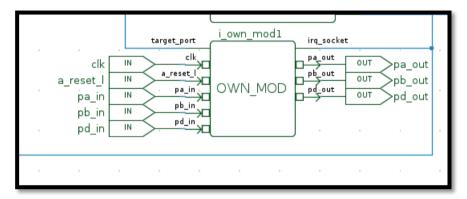

#### COSIDE: Interface modules

Own Interface module to communicate between your normal COSIDE module and the GreenSocs TLM eco system

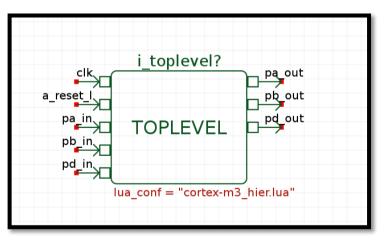

Corresponding Wrapper of the whole Cortex M3 processor exposing the interface Signals

• System configuration via LUA file provide through toplevel parameter

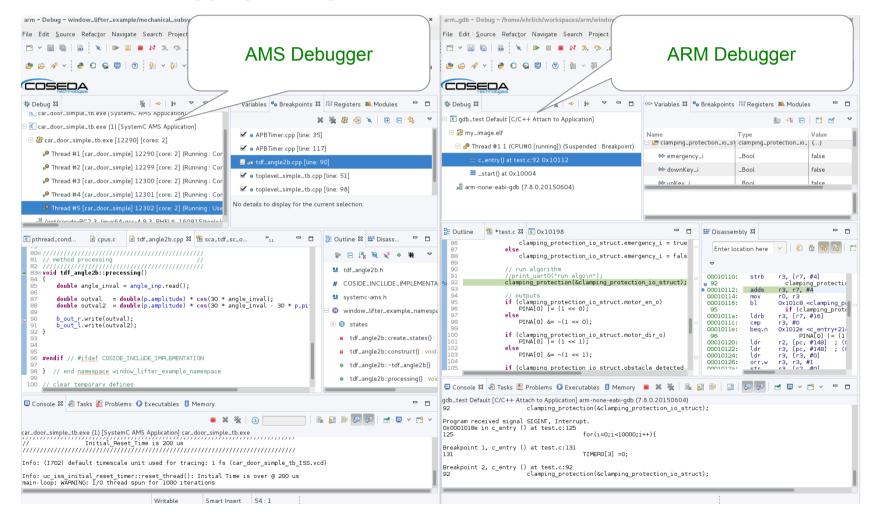

#### COSIDE: Hard- and Software debugging

- Hardware brake points within the model as well as within the ARM

- Software Debugging through remote session into the Cortex M3 core

GreenSocs

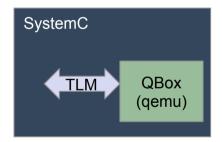

QBox

Green**Socs**

Wraps up Qemu in a TLM2-0 API such that it can be used in standard SystemC

QEMU is a generic and open source virtualizer – it covers almost all CPU architectures and achieves extremely high performance.

#### Qemu: Our Preferred source of CPU models

- Qemu is the defacto standard Virtualizer.

- Free and Open Source.

- It is over 10 years old

| 18            | 1100  | 43000   | 1000         | 989,863       |

|---------------|-------|---------|--------------|---------------|

| Architectures | CPU's | Commits | Contributors | Lines of code |

Green**Socs**

**EMU**

- GreenSocs is a key contributor:

Reverse execution and Multi-Core TCG Kernel.

- Regular committers from many organizations

#### CPU Family coverage:

|                                              | X86 | ARM | MIPS | Alpha | PowerPC | SPARC | Micro-<br>blaze | Cold-<br>fire | Cris | SH4 | Xtensa |

|----------------------------------------------|-----|-----|------|-------|---------|-------|-----------------|---------------|------|-----|--------|

| Fast<br>SW dev<br>model<br>(LT)              | ~   | ~   | ~    |       | ~       | ~     | ~               | ~             | ~    | ~   | ~      |

| Cycle<br>Accurate<br>HW dev<br>model<br>(AT) | ~   | ~   |      | ~     |         | ~     |                 |               |      |     |        |

Full list (of several hundred) available on GreenSocs.com

#### Extending Qemu for EDA virtulization

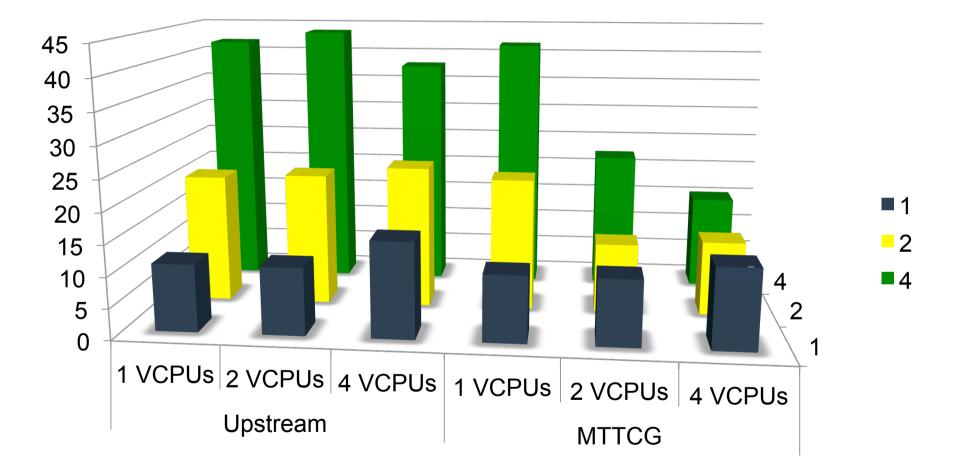

- MULTI Thread Qemu

- A massive speed improvement for Qemu to take advantage of multi-core hosts

- SystemC integration

- The ability to mix SystemC models with Qemu.

- Reverse Execution

- The ability to find a bug, and step backwards (in time) to find the source of the bug.

- GreenSocs has a fast implementation which is compatible with SystemC.

- Instruction counting and analysis features

- Enhanced counting mechanisms for memory accesses and instruction counting

#### Quick Benchmark Results for MTTCG

Green**Socs**®

#### SystemC TLM-2.0 IEEE 1666 is : The Virtual Platform Standard

• Open Source Simulator available for download from Accellera.org

QUALCOMA (intel) cādence Synopsys Graphic ARMAMDI ERICSSON INTEL Corporate members 2016

- Green**Socs** technology at the heart of TLM-2.0 standard.

- All GreenSocs interfaces use TLM-2.0

- Green**Socs** helping Accellera forge a new Model to tool standard.

- Preview available in GreenConfig.

- Our solutions are tool independent, and work with **all vendors**.

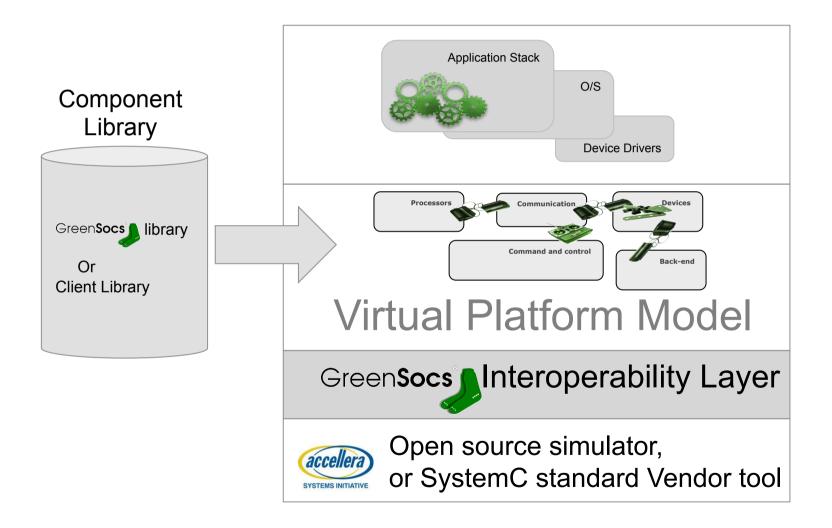

#### Model Based Virtual Platform Architecture

Green**Socs**

#### **GreenSocs SystemC Infrastructure.**

- Model Construction

- Eases building register definitions, state machines etc

- Scripting (Python)

- Model to Model communication

- Busses and routers (e.g. AMBA, PCIe, OCP, etc)

- Signals (interrupts etc)

- Serial, Ethernet, Graphics etc....

- Model to Tool communication

- Configuration, (inc Lua)

- Control (Run time re-configuration)

- Inspection (outputs and tracing).

- Model IP

- Routers,

- simple IP blocks,

- libraries (Graphics, communication)

- Tools

- Integration with Qemu, GEM5, Eclipse and other tools.

en П

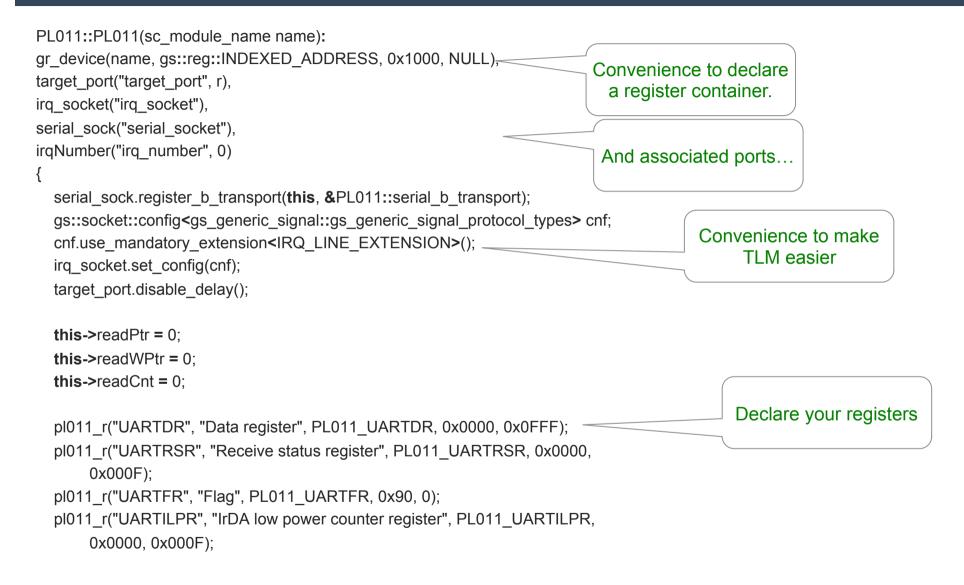

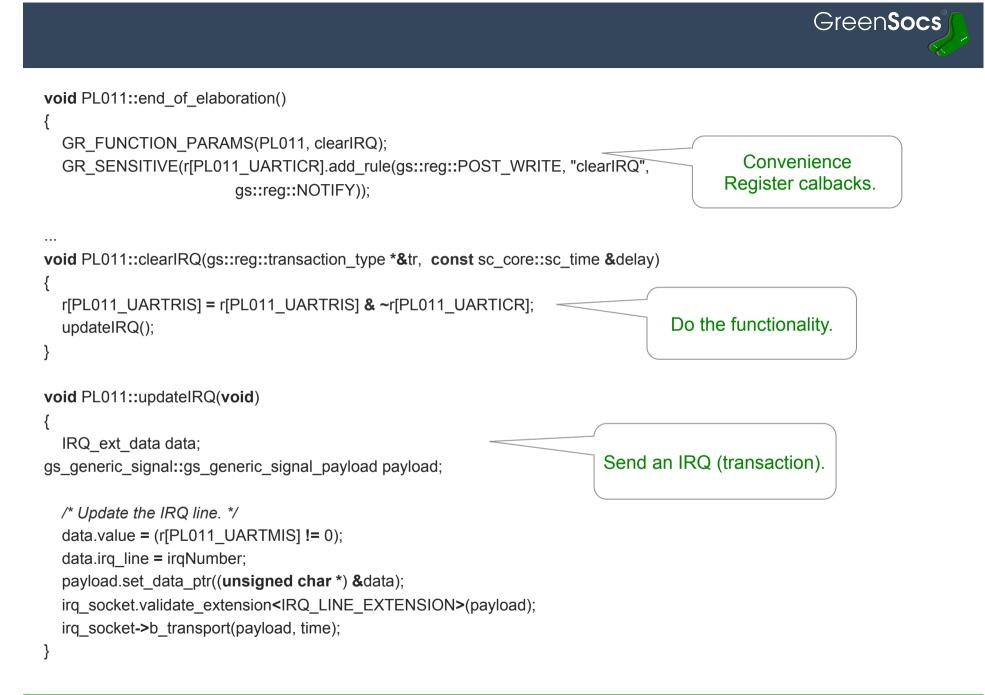

#### So, what does the code look like?

GreenSocs provides it's library, and IP under an end user license agreement to it's customers.

You receive full source, and the rights to modify and distribute that source code internally to your company free of charge.

The license is a modified BSD.

# Qbox is provided as an TLM model from <a href="http://greensocs.com/">http://greensocs.com/</a>

It is a free download, and neither you, nor any customer is required to pay any license.

It is licensed under the GPL You may use it freely, if you distribute code based on it, you must do so in source form.

You should write your SystemC models to respect the TLM-2.0 API's. You should allow your customers the choice of which CPU model to use. One (free) choice is a Qbox model.

Nobody (apart from GreenSocs) should be distributing Qbox.

#### Your product Her tool choice Is not his choice Must not force your choice!

## Is their component

Models **must be tool independent** They must use the **Standard** interfaces

#### GreenSocs : principle offers

#### **Consultancy and Services**

The **Experts** in **Virtual platforms**: Creation, deployment, integration

Tool independent – vendor neutral. Allow us to guide you to **success**

#### **MODEL DEVELOPMENT**

Virtual Platforms based integrated development environments, for CoTs or specialist devices,

ready for your software engineers to be productive.

All models adhere to STANDARDS

All model source provided.

#### **OPEN SOURCE DEVELOPMENT**

Adding to the existing open source tools and models.

'Upstreaming' and dissemination

## www.greensocs.com

mark@greensocs.com