# Optimization of Complex Circuits at System Level

#### **MunEDA Corporate Overview**

EDA Software Vendor – Tools SPT & WiCkeD<sup>™</sup> for Migration, Sizing and Verification of full custom nanometer IC designs.

- Worldwide Sales & Support Offices in USA, Korea, China, Taiwan, Japan, UK, Ireland, Scandinavia, South America

- Worldwide Customer & Partner Base with Semiconductor IDMs, Fabless Design Houses & Foundries

For more information visit <u>www.muneda.com</u>

#### MunEDA EDA Solutions for Full Custom IC Migration, Sizing & Verification

MunEDA – Comprehensive EDA Tools for Migration, Sizing and Verification of Nanometer Custom IC Designs

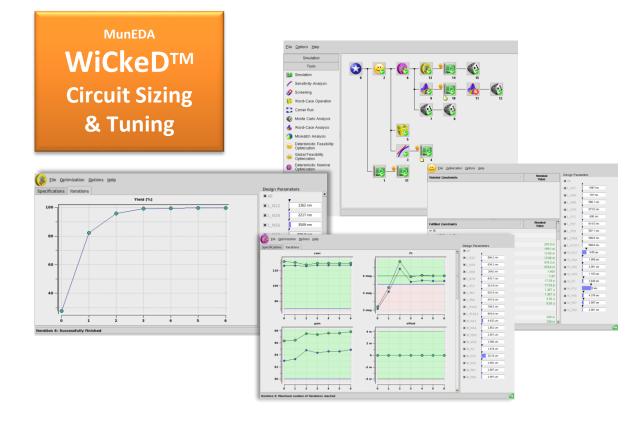

MunEDA WiCkeD<sup>TM</sup> Circuit Sizing & Tuning

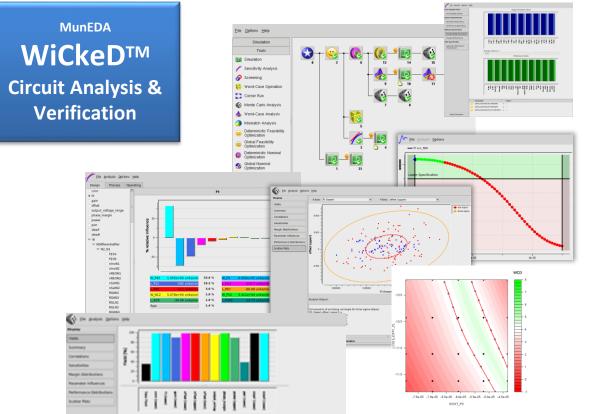

#### MunEDA WiCkeD<sup>TM</sup> Circuit Analysis & Verification

**Circuit Sizing & Tuning with WiCkeD<sup>TM</sup>** Meet performance specifications over all types of variation, design and operation parameters with MunEDA sizing & optimization tools

Circuit Verification with WiCkeD<sup>™</sup>

Analyze and verify your circuit designs for constraints, performance specifications, operating and process parameters, global and mismatch variation, reliability and others

© Copyright by MunEDA GmbH - All rights reserved - www.muneda.com

## Mun<mark>EDA</mark>

#### **Empowering Innovation**

## MunEDA WiCkeD<sup>™</sup> Tool Suite for Circuit Sizing & Tuning

#### **Selected Features:**

- Circuit Constraint & Feasibility Optimization

- Deterministic Nominal Circuit Optimization

- Global Nominal Circuit Optimization

- Discrete Circuit Optimization

- Yield Optimization

- Circuit sizing under consideration of degradation and reliability effects

- Circuit Design History & Database

- Parallel simulation environment (supporting industry-standard SPICE simulators)

- Multitestbench-Support

- MunEDA WiCkeD<sup>™</sup> Circuit Sizing & Tuning: simulation-based tools to improve and optimize custom circuits

- Targets constraint fulfilment, performance specifications, robustness, targets for yield, area, stability, timing, power, reliability, aging, degradation, stress, self heating and more !

## Mun<mark>EDA</mark>

#### **Empowering Innovation**

## MunEDA WiCkeD<sup>™</sup> Tool Suite for Circuit Analysis & Verification

#### **Selected Features**

- Parallel simulation environment (supporting industry-standard SPICE simulators)

- Multitestbench-Support

- Circuit Constraint Feasibility Check

- Circuit Sensitivity Analysis for performances, gain, frequency, slewrates, power, stability, area, others

- Fast PVT & Operating Corner Analysis: influence of corner cases on given circuit performances

- Parameter Screening

- Fast & Enhanced Monte Carlo Analysis (3-5 sigma)

- High Sigma Worst Case Analysis (6-9 sigma)

- Importance Sampling & Robustness Verification

- Global and local (mismatch) variation and yield analysis

- Reliability & aging analysis for degradation effects

- Yield plot sweeps for global variation

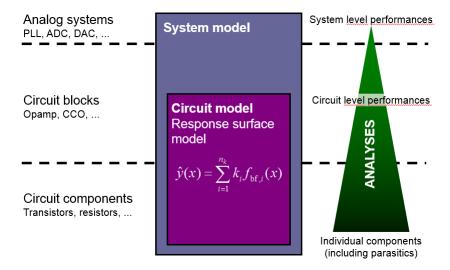

- RSM Circuit Modelling & Model Generation

- MunEDA WiCkeD<sup>™</sup> Circuit Analysis & Verification: comprehensive and powerful tools for simulation-based analysis and verification of Custom IC

- Targets circuit constraints, design parameters, PVT, operating corners, specifications, sensitivities, correlations, process dependencies, sweeps, global and mismatch variation, Monte-Carlo, Worst-Case, High Sigma, reliability and more !

#### **Empowering Innovation**

# Mun<mark>EDA</mark>

## **Motivation**

## **7** Complexity

- Analysis and optimization requires multiple simulations

- Works well with simulation times in the range of seconds/minutes

- Successfully applied with spice simulations at block level (OpAmps, Bandgaps, Memory cells, standard cells, etc.)

- For more complex circuits with simulation times of several hours (i.e. PLL, ADC) → no fun

Source of graphics: Wikipedia, http://readingrat.net/

## Mun<mark>EDA</mark>

## **Motivation**

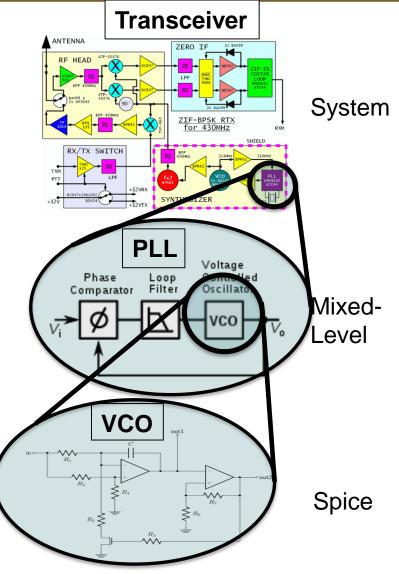

#### オ Approaches

- Methodologies to create behavioural models of complex circuits

→ stuck in tradeoff between effort to create the model vs. accuracy

- Methodology to break up in blocks, model and simulate mixed-mode

→ cumbersome, mixed-tool environment

### **オ** Requirements

- Simplified creation of AMS Models

- Mixed-Level Simulation for optimization, verification, and debugging

### Solution via Coside

- System C / System C AMS enables simulation of complex circuits X times faster than spice level

- Coside practical tool for modeling, mixed-simulations, and debugging

© Copyright by MunEDA GmbH - All rights reserved - www.muneda.com

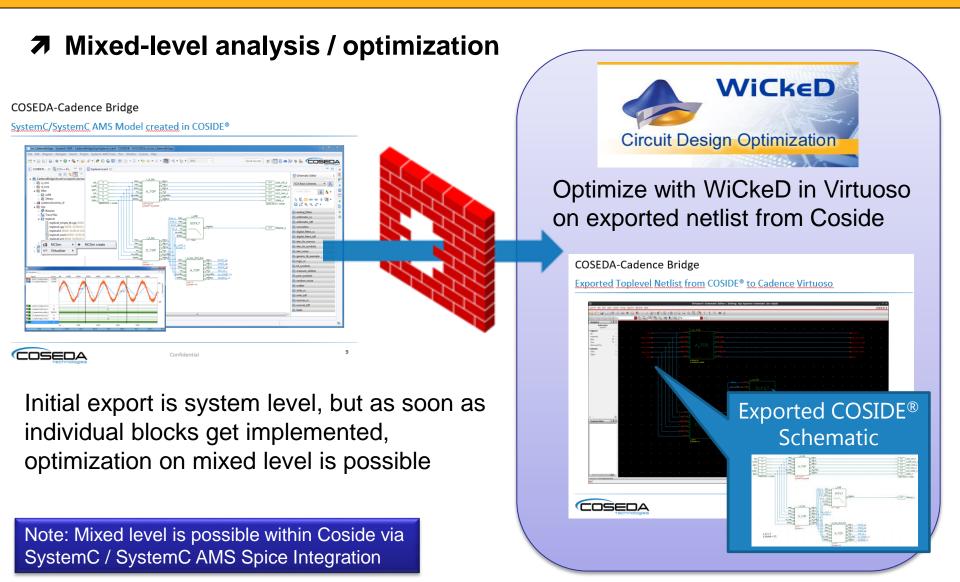

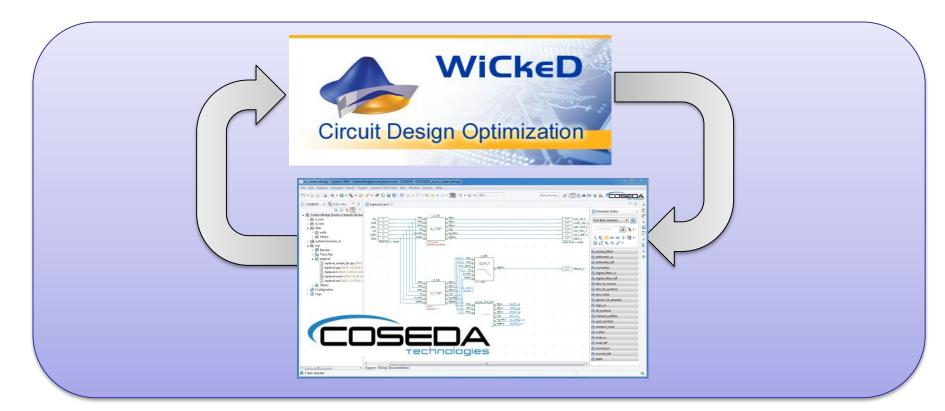

#### **Mixed-Level Optimization**

Mixed-level optimization within normal EDA design framework

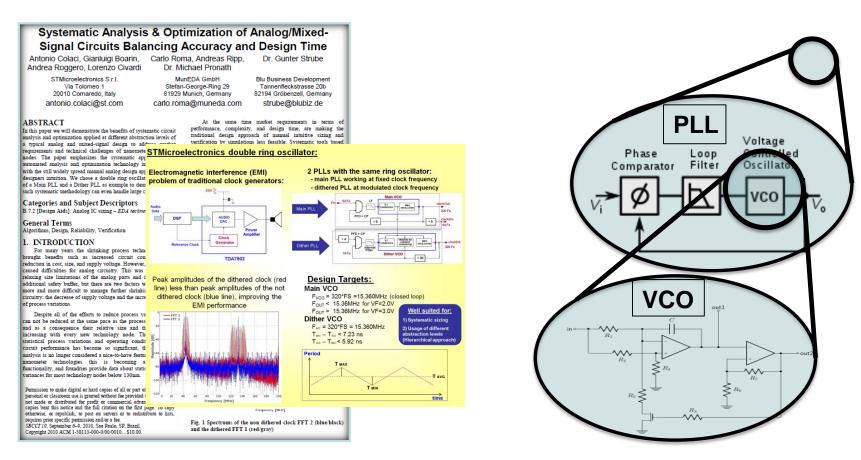

# **オ** STM paper in 2010 →optimization of VCO within Dithered PLL

Using Coside to Apply Optimization to System

- **7** Full hierarchcial flow: use WiCkeD @ system level

- WiCkeD / Coside interface → optimize using SystemC simulation

- Mixed level is possible by Coside SystemC / SystemC AMS Spice Integration

- Optimization can include "other components" (mechanical, etc.)

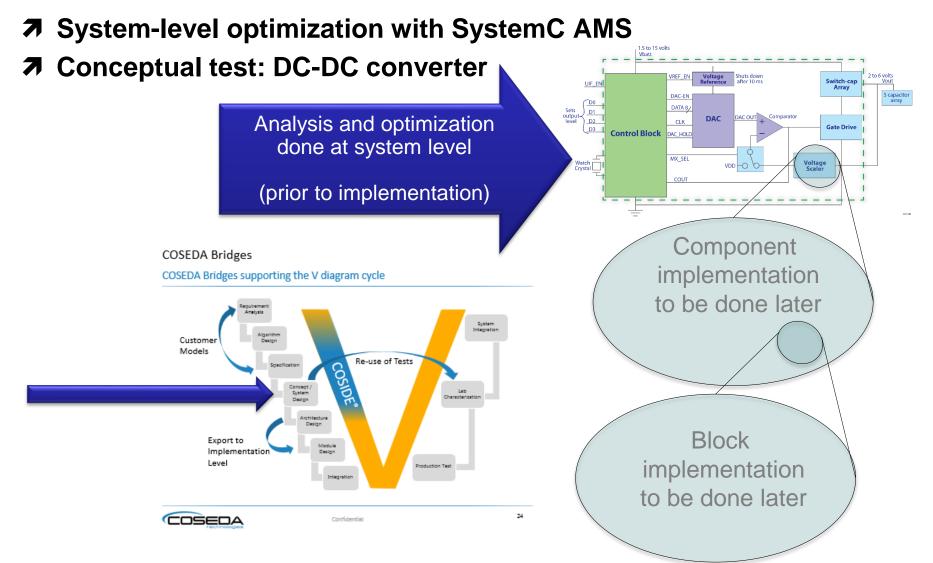

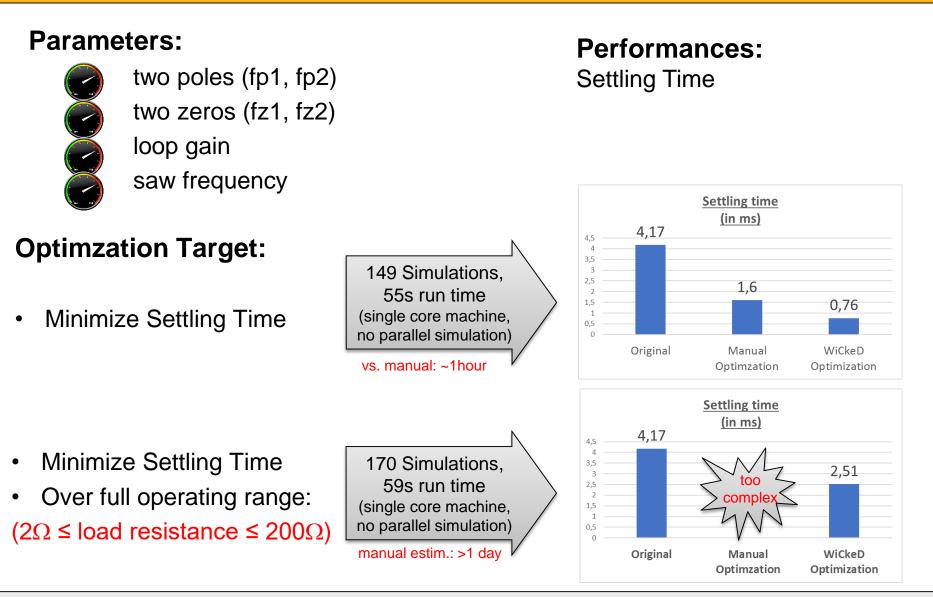

#### System-Level Optimization

Source of graphic: https://www.ridgetopgroup.com/products/semiconductors-for-critical-applications/instacell-ip-core-library/dcdc-converter/

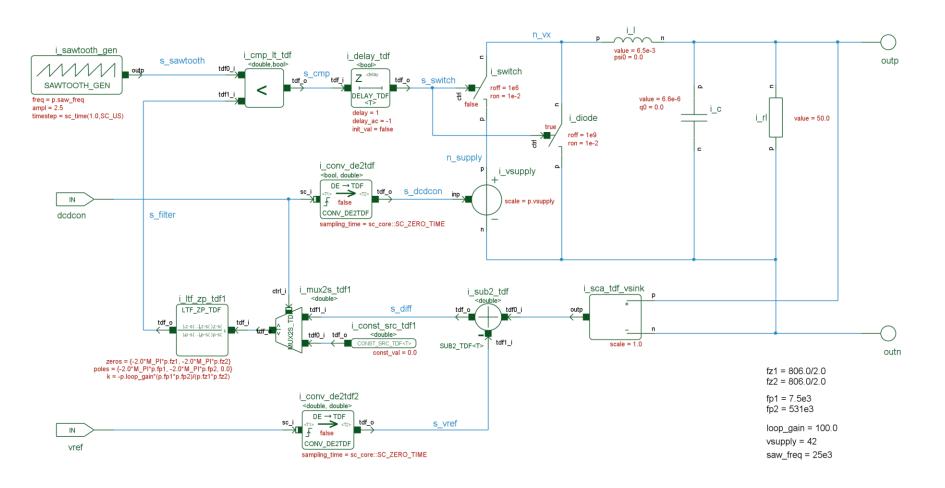

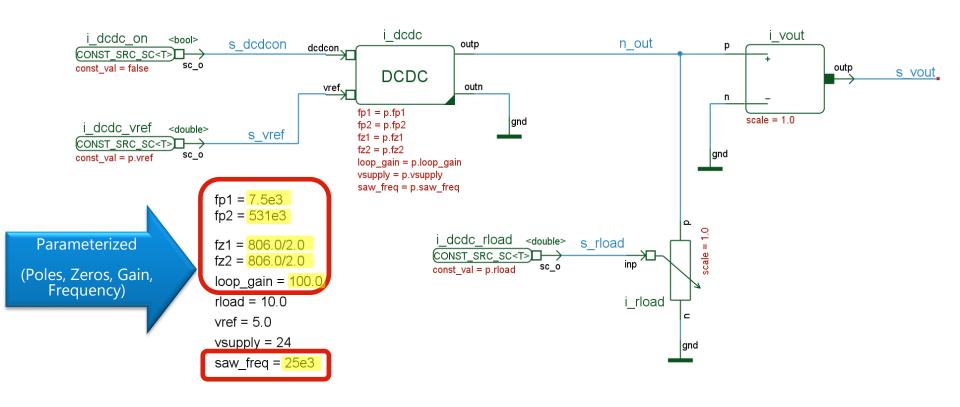

#### DCDC Systemlevel model

#### Testbench

#### Input parameter file

```

//parameter for optimization

fp1 = 7.5e3; //loop filter poles and zeros

fp2 = 531e3;

fz1 = 403.0;

fz2 = 403.0;

loop_gain = 10000.0; //loop gain

saw_freq = 25e3; //sawtooth generator frequency

```

```

//configuration parameter

rload = 10.0; //load resitance

vref = 5.0; //reference voltage

vsupply = 24; //supply voltage

```

```

trace_file="onchar.dat"; //trace file

```

#### //measurement configuration

```

settling_tolerance=0.1; // +/- vref to be consdered as inbound

settle_time=5e-3; // inbound time to be considered as settled

max_settle_time=50e-3; //maximum measurement time -> if not

settled within this time -> unsettled

```

#### Testsequence (to calculate settling time)

```

case INBAND:

void dcdc_tb_stim_onchar::stimulus_sequence()

if(fabs(vout-dut_p->vref)>s.settling_tolerance) cstate=OUTBAND;

{

std::cout << sc core::sc_time_stamp() << " Stimulus sequence started..." << std::endl;</pre>

if((ctime-last_outtime)>s.settle_time) //settled

const sc_core::sc_event& change_ev=s.vout.get_new_value_event(); /* get event for dcdc out*/

settling time=ctime-dcon time-s.settle time;

s.settled=true;

wait(1.0,SC MS);

finished=true:

break;

s.dcon.set_value(true); //switch converter on

}

double dcon_time=sc_time_stamp().to_seconds();

if(finished)

check state cstate=OUTBAND;

std::cout << "Settling time: " << settling time << std::endl;

std::cout << "overshot: " << max_overshot << std::endl;

std::cout << "undershot: " << max undershot << std::endl;</pre>

double last outtime=0.0;

double settling_time=1e9;

break;

double max_overshot=0.0;

double max_undershot=0.0;

bool finished=false;

if(sc_time_stamp().to_seconds()-dcon_time > s.max_settle_time)

bool shot=false;

std::cout << "Not settled" << std::endl;</pre>

break;

while(true)

{

wait(change_ev); /* continue if next dcdc out value available*/

double vout= s.vout.get_value();

std::ofstream fstr("dcdcon result.dat");

fstr << std::setprecision(15);</pre>

if(vout > dut_p->vref) shot=true; //if once over vref -> start shot measurement

if(!finished)

fstr << "Settling time = " << " " " << ";" << std::endl;

fstr << "overshot = " << max_overshot << std::endl;

fstr << "undershot = " << max_undershot << std::endl;</pre>

if(shot)

if(vout-dut_p->vref>max_overshot) max_overshot=vout-dut_p->vref;

if(vout-dut_p->vref < max_undershot) max_undershot=vout-dut_p->vref;

else

}

fstr << "Settling time = " << settling_time << ";"<< std::endl;</pre>

fstr << "overshot = " << max_overshot << ";"<< std::endl;

fstr << "undershot = " << max_undershot << ";"<< std::endl;</pre>

double ctime=sc_time_stamp().to_seconds();

switch(cstate)

fstr.close();

{

case OUTBAND:

std::cout << sc_core::sc_time_stamp() << " Stimulus sequence finished." << std::endl;</pre>

last outtime=ctime;

wait(1.0,SC MS);

if(fabs(vout-dut_p->vref)<s.settling_tolerance) cstate=INBAND;</pre>

sc_core::sc_stop();

break:

```

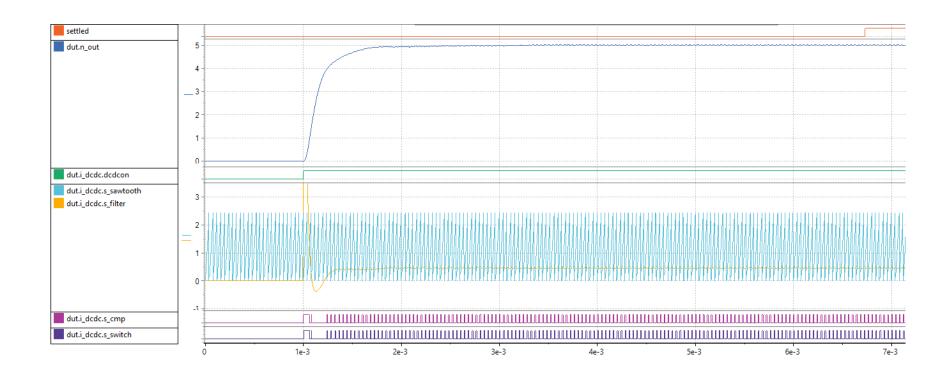

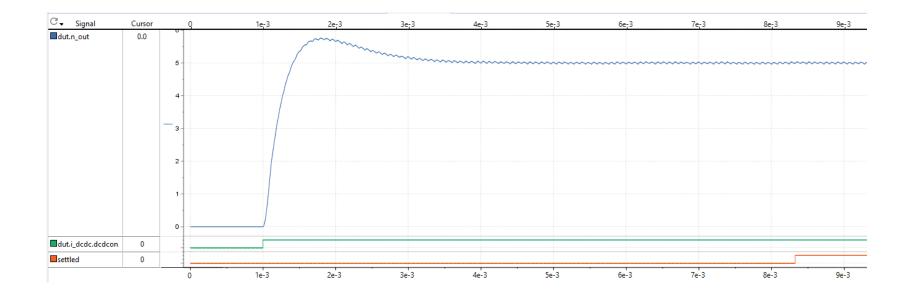

#### Example for simulation result

#### Simulation Result

#### **Optimization Example**

## **Mun**EDA

#### Summary

- Simple demonstrator showed tool coupling example

- Optimization worked fast and showed good results (applicable to far higher complexity than this simple demonstrator)

- ➔ Interesting learnings / observations from this simple example:

- Difference between implementation and system level not just different abstraction: Parameters at system level are not physical dimensions (as transistor widths)

- Parameters at system level can be performances (results) of sub-blocks

→ completely new field of applications opening up

## **7** Outlook:

- Same environment can be extended to more complex circuits

- Interfaces at system level enable cross domain simulation (analog/digital, hardware, software, embedded, mechanical, etc.)

## Thank You !