### AMS Timing Closure with Coside Using timing-aware models and static analysis techniques

Guillermo Conde, Infineon Technologies Austria 09.11.2021

restricted

|   | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

| 1 | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

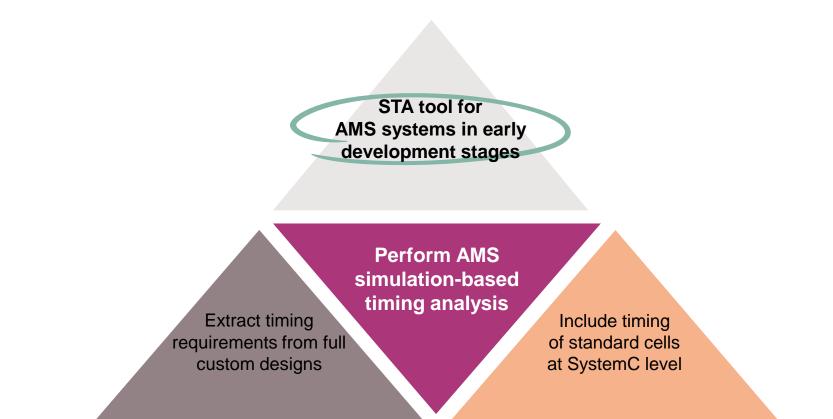

#### Introduction

#### **Timing Closure**

process by which a logic design (sequential + combinatorial gates) is modified to meet its timing requirements.

#### Semi-custom designs using STA

- Timing requirements are translated into static timing constraints to the EDA tool.

Timing Closure in AMS systems

- Models including accurate

No timing requirements in place.

characterization

- Models do not include any timing characterization.

- Timing issues detected very late in development

## Infineon

| 1 | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

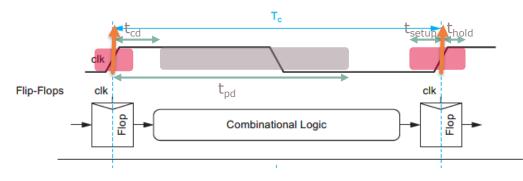

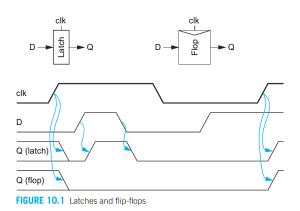

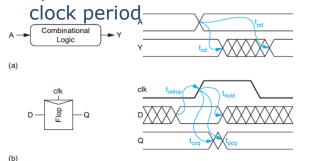

### Timing basics in digital systems

Most common sequencing elements are latches and flip-flops

- > Basic timing contraints and delays

- > Worst case scenario known including PVT

- Systematic method to guarantee proper timing (STA)

- Systems insensitive to PVT variations once timing is guaranteed

Digital flow rules: Synchronous systems based on FFs and constant

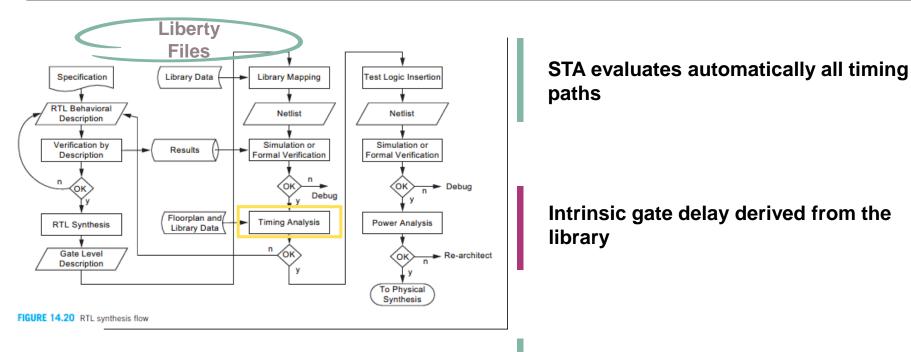

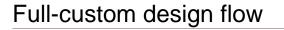

#### Semi-custom design flow

Source: CMOS VLSI Design, Neil H.E Weste

Loads are either estimated statistically or derived from the floorplanning.

| 1 | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

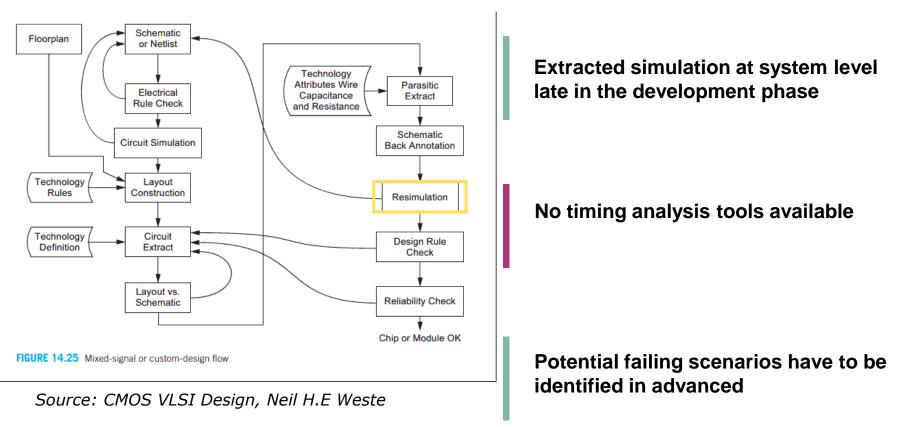

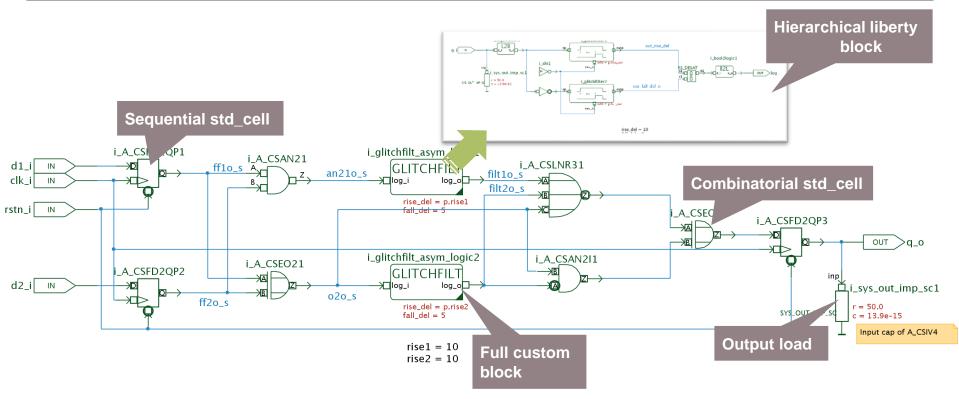

### AMS system components

| 1 | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

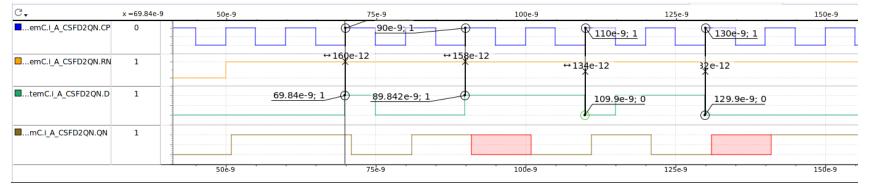

### Timing-aware models

- > System C models with 4-value data types

- > Delay included

- > Time stamps taken at every event

- > Automatic checks on

- Setup and hold time

- Reset recovery and removal

- Minimum Pulse Width

| Delay Path                            |     | Load | Capad | itance | [fF]     |  |  |

|---------------------------------------|-----|------|-------|--------|----------|--|--|

| [ps]                                  | 5   | 10   | 25    | 50     | 250      |  |  |

| $CP\Uparrow\RightarrowQN\Downarrow$   | 403 | 422  | 473   | 552    | 1.18e+03 |  |  |

| $CP \Uparrow \Rightarrow QN \Uparrow$ | 443 | 463  | 519   | 613    | 1.35e+03 |  |  |

| RN ↓ ⇒ QN ↑                           | 266 | 286  | 343   | 436    | 1.18e+03 |  |  |

|                   | Constraint [ps] |

|-------------------|-----------------|

| Check             | typ             |

| D ↓ setup CP ↑    | 133             |

| D ↓ hold CP ↑     | 14.9            |

| D ☆ setup CP ☆    | 159             |

| D ↑ hold CP ↑     | 24.2            |

| RN    recovery CP | -261            |

| RN 🕆 removal CP 🕆 | 263             |

| MPW    | value [ps] |

|--------|------------|

| CP (L) | 173        |

| CP (H) | 156        |

| RN (L) | 274        |

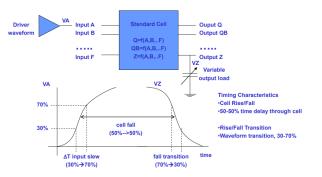

#### Liberty Files

- > Open Source ASCII format to specify:

- PVT Characterization

- Area

- Timing

- Power

- Noise

- > Cell delays/constraints depending on:

- Input slew

- Output load

Joseph A. Elias, Ph.D, University of Kentucky, Adjunct Professor, ECE Dept; Cypress Semiconductor MTS

| pin(Q | <pre>N) {     direction     capacitance     max_capacitance     min capacitance</pre> | : output;<br>: 0;<br>: 0.256;<br>: 0.001; |                                                                                                                                  |                                                                                                                        |                                       |                                                                                                                                 |                                 |                                                                                                                                  | Delay D                                                     | ata                                                                                                       |     |                                                                                               |                                            |                                      |         |                                                                                                                       |  |

|-------|---------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------|--|

|       | related_ground_pi                                                                     |                                           |                                                                                                                                  |                                                                                                                        |                                       |                                                                                                                                 |                                 | I                                                                                                                                | Delay Pa                                                    | ath                                                                                                       |     | Load                                                                                          | Capac                                      | itance                               | [fF]    |                                                                                                                       |  |

|       | related_power_pin<br>function                                                         | : VDD;<br>: "IQN";                        |                                                                                                                                  |                                                                                                                        |                                       |                                                                                                                                 |                                 |                                                                                                                                  | [ps]                                                        |                                                                                                           | 5   | 10                                                                                            | 25                                         | 50                                   | 250     |                                                                                                                       |  |

|       | power down functi                                                                     |                                           |                                                                                                                                  |                                                                                                                        |                                       |                                                                                                                                 |                                 |                                                                                                                                  |                                                             | QN ↓                                                                                                      | 403 | 422                                                                                           | 473                                        | 552                                  | 1.18e+0 | 3                                                                                                                     |  |

|       |                                                                                       |                                           |                                                                                                                                  |                                                                                                                        |                                       | _                                                                                                                               |                                 |                                                                                                                                  |                                                             | QN 🏦                                                                                                      | 443 | 463                                                                                           | 519                                        | 613                                  | 1.35e+0 | 3                                                                                                                     |  |

|       | /* characterizati<br>/* characterizati                                                |                                           |                                                                                                                                  |                                                                                                                        |                                       |                                                                                                                                 |                                 |                                                                                                                                  | RN↓⇒                                                        | QN 🏠                                                                                                      | 266 | 286                                                                                           | 343                                        | 436                                  | 1.18e+0 | 3                                                                                                                     |  |

|       | index_2(<br>values(                                                                   | pe :<br>(slp_load) {<br>0.001000          | CP";<br>rising_edge'<br>0.002000<br>0.389638<br>0.439651<br>0.453825<br>0.596413<br>0.554214<br>0.601872<br>0.627935<br>0.626252 | 0.050000<br>0.004000<br>0.0398695<br>0.433522<br>0.4625470<br>0.515470<br>0.563274<br>0.610933<br>0.636996<br>0.035313 | · · · · · · · · · · · · · · · · · · · | 0.100000<br>0.008000<br>0.414765<br>0.429078<br>0.43594<br>0.478952<br>0.579345<br>0.579345<br>0.627006<br>0.653072<br>0.651391 | ,<br>,<br>,<br>,<br>,<br>,<br>, | 0.250000<br>0.016000<br>0.443268<br>0.457581<br>0.47800<br>0.507455<br>0.560044<br>0.607855<br>0.6675513<br>0.681586<br>0.679906 | , 0.6<br>, 0.4<br>, 0.5<br>, 0.5<br>, 0.6<br>, 0.6<br>, 0.7 | 600000<br>332000<br>195594<br>609905<br>13421<br>559781<br>512372<br>560180<br>707849<br>733927<br>732251 |     | 0.06400<br>0.59668<br>0.6109<br>0.6608<br>0.71340<br>0.71340<br>0.80894<br>0.83503<br>0.83335 | 34 ,<br>17<br>13 ,<br>55 ,<br>74 ,<br>32 , | 0.79<br>0.81<br>0.83<br>0.86<br>0.91 | 567 ,   | 2.40000<br>0.25600<br>1.19806<br>1.21237<br>1.23288<br>1.26226<br>1.31484<br>1.36264<br>1.41034<br>1.43642<br>1.43474 |  |

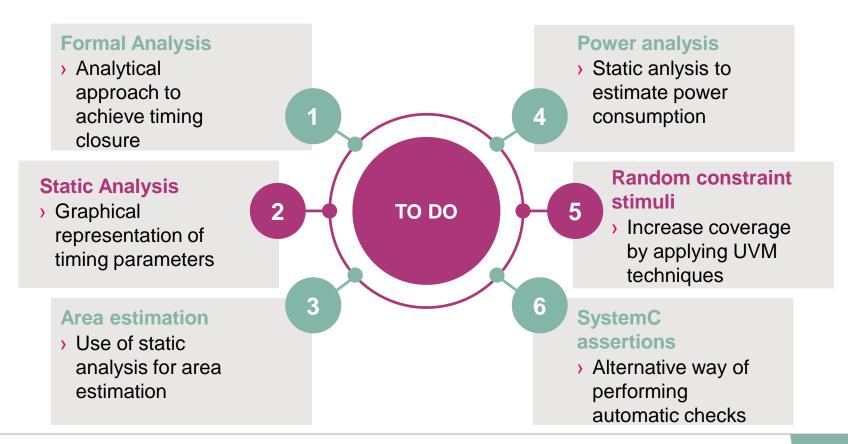

| 1 | Introduction                          | 3  |

|---|---------------------------------------|----|

| 2 | Timing in Synchronous Digital Systems | 6  |

| 3 | Timing in AMS Systems                 | 9  |

| 4 | The Liberty Block                     | 12 |

| 5 | Coming Next                           | 17 |

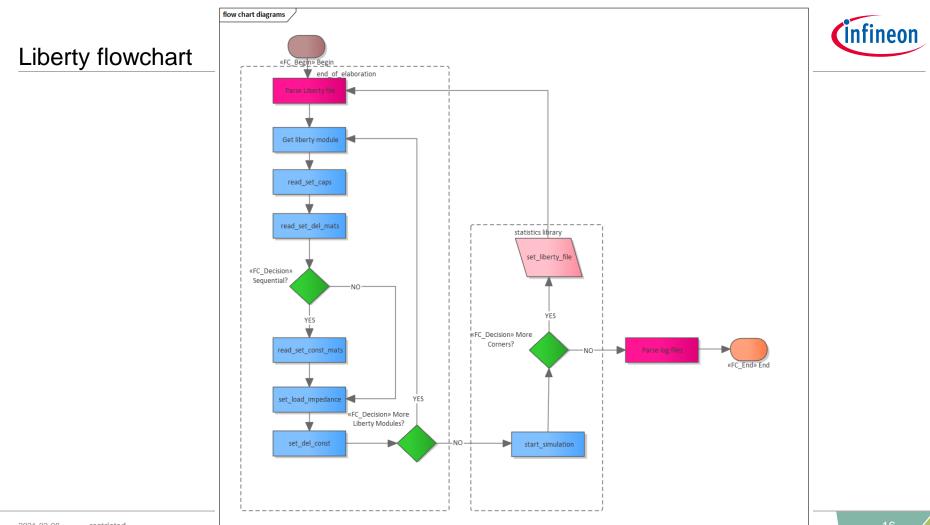

### Automatic timing calculation > Assignment of delay and constraints directly from Liberty files into the Liberty blocks AMS timing-aware simulations Automatic detection of scenarios with timing violations **Multi-corner simulations** Timing-aware simulations over corners via statistical library

## Part of your life. Part of tomorrow.