SYSTEMC AMS PLATFORM FOR RADAR: THE RF BIST

### SYSTEM VALIDATION CONCEPT WITH COSIDE®

Dominique Delbecq (NXP), Michel Vasilevski (Seamless Waves)

OCTOBER, 2020

PUBLIC

#### OUTLINE

- System C-ams platform for RADAR transceiver system exploration : reason for the choice of this platform

- Description of the pilot : BIST for RADAR

- Development of the models

- An example of a 77GHz simulation with ARM control

- Conclusion and some comparison

# SystemC platform for RADAR system exploration

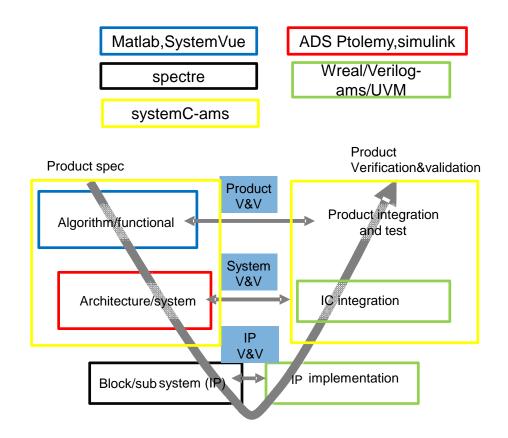

#### SYSTEMC-AMS PLATFORM TO MANAGE COMPLEXITY

- Automotive RADAR market is requiring more complexity (imaging radar) and more integration (cost)

- A performant radar system is a smart combination of **heterogeneous** . systems : PCB/antenna, MMW, RF, analog, digital, processing, software

- **Smart Partitioning (analog=>digital, hardware => software)** allows area reduction and flexibility (software Design RADAR). However the system exploration is difficult to validate by simulation without virtual simulation platform.

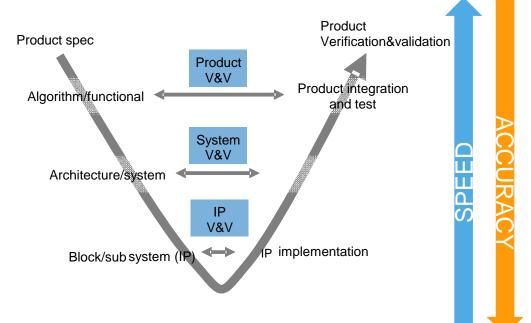

- There is today no virtual platform simulation that is capable of supporting a **continuity of check along the V development** (from algorithm to validation)

- Also all the platforms in development are **costly** to support (tool cost, . people expertise)

- The serial approach prevent "parallelization" of the activities.

- **The virtual platform** should allow to model *RF imperfections*, simulate control loops (RF/digital/software) while keeping simulation time fast

NP

#### SystemC-ams is a language and not a tool that can be integrated in many platform. Could be the best trade-off accuracy/speed

|                                             | SystemC-ams                                          | Other platforms                                                 |

|---------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------|

| speed                                       | Compiled language                                    | Simulink, Ptolemy,<br>Verilog-ams are pretty<br>slow simulation |

| RF modeling and flexibility in analog model | Coside models support<br>envelop type                | Proprietary models for ADS                                      |

| Manage time domain and control loops        | Tdf models                                           | Limitation with Matlab                                          |

| Multi platform                              | Well suited with software                            | Heavy Co-simulation                                             |

| cost                                        | Almost free                                          | Market tools are expensive                                      |

| Investment                                  | Need investment to develop libraries and competences | Libraries available                                             |

NP

# RADAR BIST

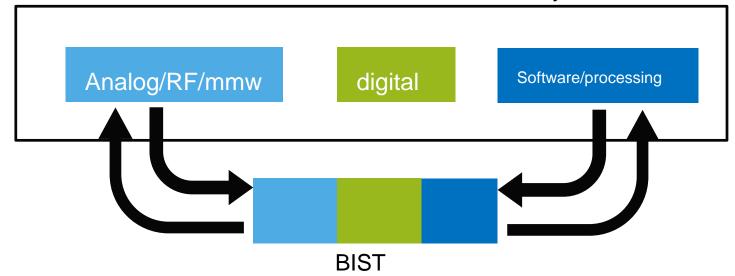

#### **BIST IN RADAR TRANSCEIVER**

- **BIST (Build-in self test)** corresponds to additional circuitry in a circuit that allows to test functional circuitry (injecting/measuring)

- It is more and more important for :

- Reducing production test cost by embedding tester on chip

- > Improving the **safety** coverage (ASIL for automotive) by guaranteeing performance over the life time

- > Allow continuous **calibration** of analog/RF in advanced cmos design

Sub-system Radar

#### SYSTEM-AMS WITH BIST

BIST is a good exercise for SystemC-ams platform

This project was a collaboration between :

- NXP

- SeamlessWaves (for models writing)

- Coseda (Coside enhancement)

System simulation experiment

- BIST for RADAR receiver

- BIST for RADAR transmitter

- 77GHz PLL fracN generation controlled by ARM

|                                             | SystemC-ams                                     |

|---------------------------------------------|-------------------------------------------------|

| speed                                       | Yes                                             |

| RF modeling and flexibility in analog model | RF&MMW<br>Need noise,linearity,<br>impairements |

| Manage time domain and control loops        | Yes !!                                          |

| Multi platform                              | Yes!!                                           |

| Validation of software                      | Yes                                             |

| Complexity of system                        | Yes                                             |

# SystemC AMS models

#### SYSTEMC AMS MODELING WITH COSIDE

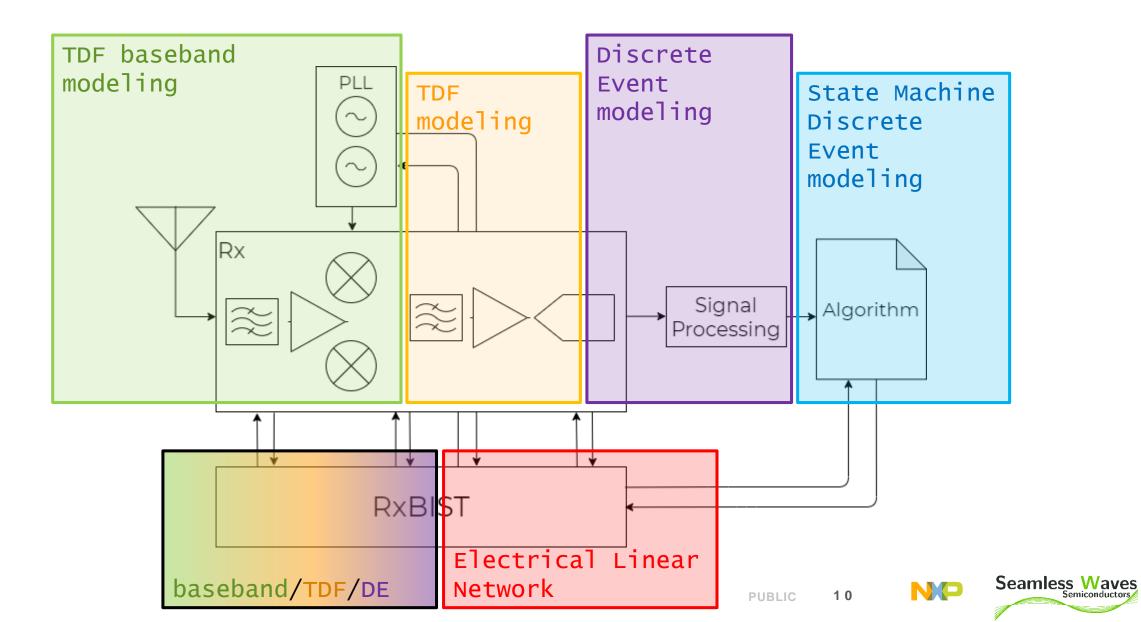

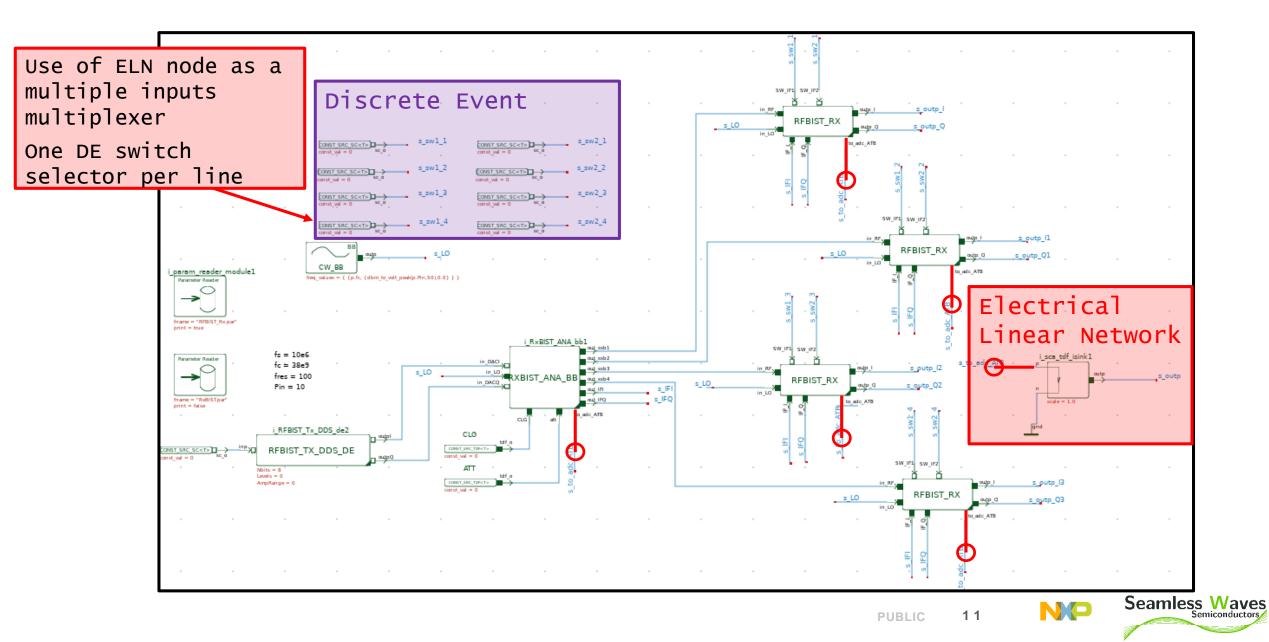

### Heterogeneous modeling

- TDF COSIDE baseband : RF signal path

- TDF standard : IF Analog signal path

- ELN (Electrical Linear Network) : Sensed Power for BIST purpose

- Discrete Event : Discrete Tuning signal

- State Machine Discrete Event : Algorithm

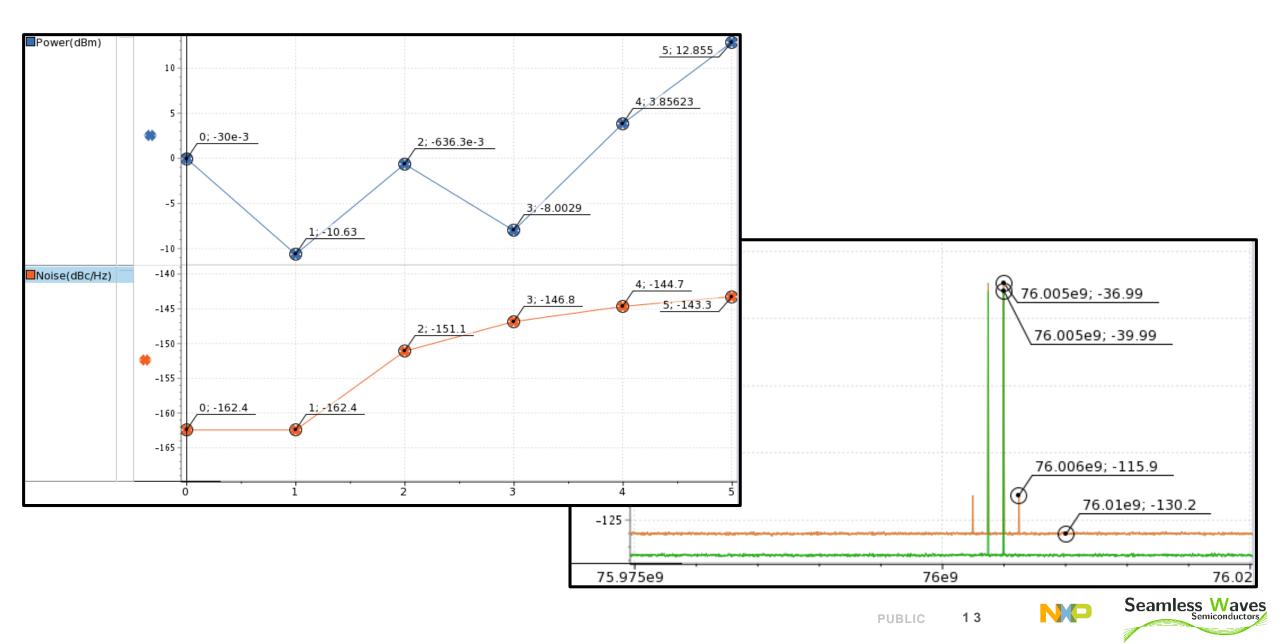

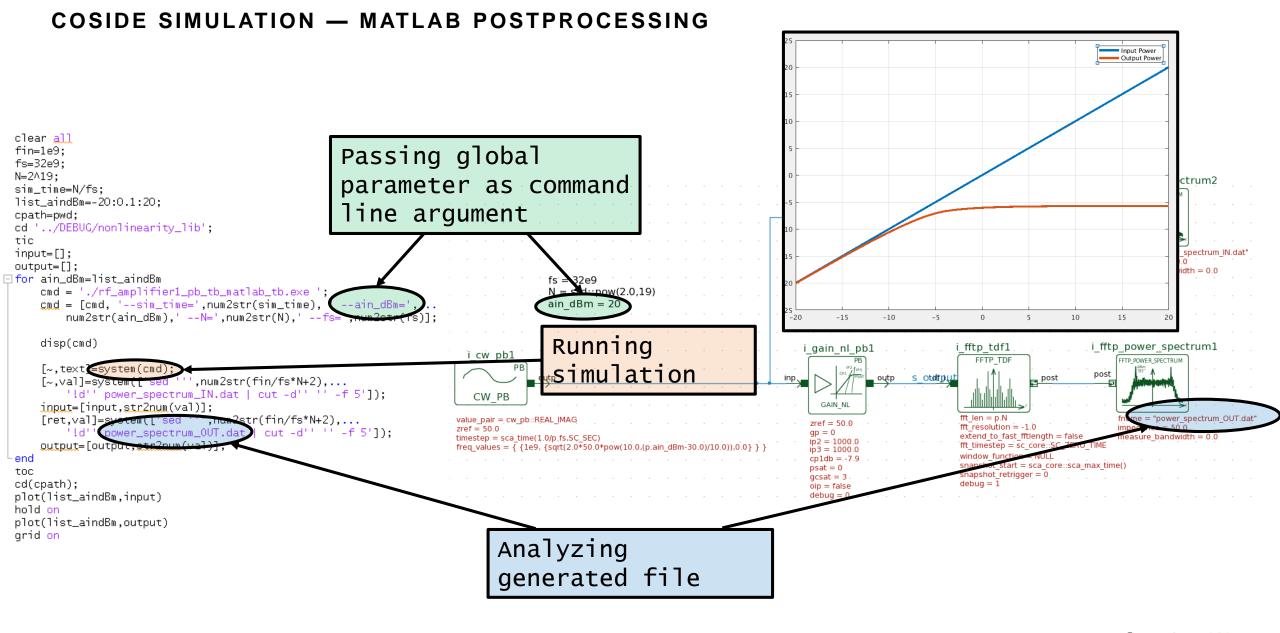

### Simulation and postprocessing with COSIDE

- Embedded COSIDE graphical visualization: time domain and frequency domain

- Python scripting for specific postprocessing computation

- Link with Matlab/Octave software

- Use of parameters configuration file

NC

#### **HETEROGENEOUS MODELING**

#### **HETEROGENEOUS MODELING**

#### IMPLEMENTED COMPONENT SPECIFICATIONS

#### **RF Amplifier**

|--|

Input Resistance (Ohm)

Output Resistance (Ohm)

Temperature (Kelvin)

Gain (dB)

Saturation Power (dBm)

Gain Compression at Saturation (dB)

Output 1dB Compression Point (dBm)

Noise Figure (dB)

AM Smoothness

**PM** Transition

PM Smoothness

**PM Scaling**

AM Noise vs Frequency (Hz,dBc/Hz)

PM Noise vs Frequency (Hz,dBc/Hz)

#### IQ DAC

PLL

$\sim$

$\sim$

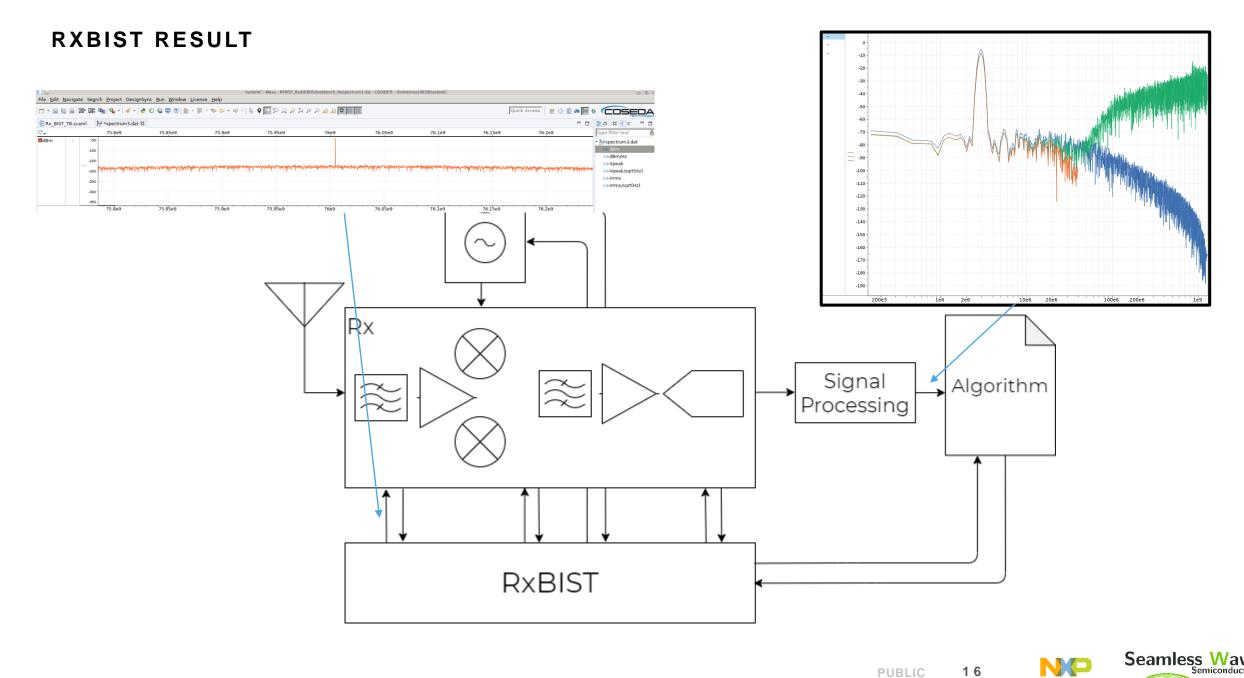

**RxBIST**

Rx

Description

Voltage Reference (V)

Number of Bits

Integral Non-Linearity Number of Sigma for INL

#### **IQ Modulator**

PUBLIC

|                     | Description                                                                              |  |  |

|---------------------|------------------------------------------------------------------------------------------|--|--|

|                     | Input Resistance (Ohm)                                                                   |  |  |

|                     | Output Resistance (Ohm)                                                                  |  |  |

|                     | Temperature (Kelvin)<br>I/Q Amplitude Error (dB)                                         |  |  |

|                     | I/Q Phase Error (deg)<br>I Amplitude Leakage referenced to LO-I (dBc)                    |  |  |

|                     | Q Amplitude Leakage referenced to LO-Q (dBc)<br>I Phase Leakage referenced to LO-I (deg) |  |  |

|                     | Q Phase Leakage referenced to LO-Q (deg)<br>Output Power (dBm)                           |  |  |

|                     | Reference Voltage (V)                                                                    |  |  |

| Signal<br>Processir | Algorithm                                                                                |  |  |

#### EMBEDDED GRAPHICAL VISUALIZATION

#### PUBLIC 14

NP

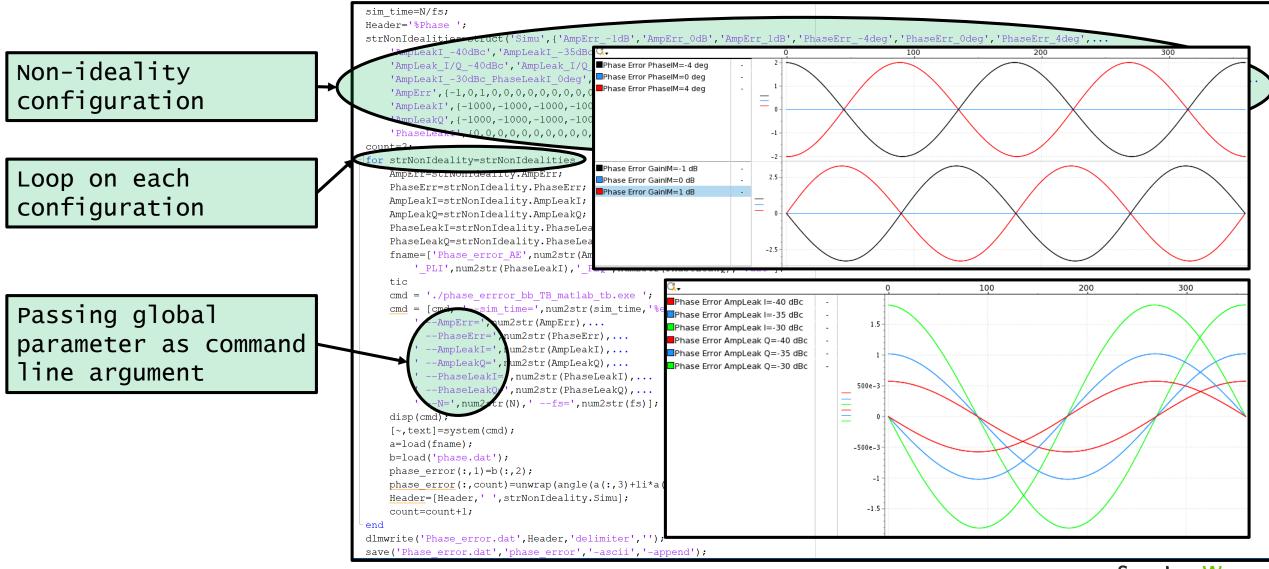

#### BATCH COMMAND LINE SPECIFICATION EXECUTION

NP

# PLL-ARM example

#### PUBLIC

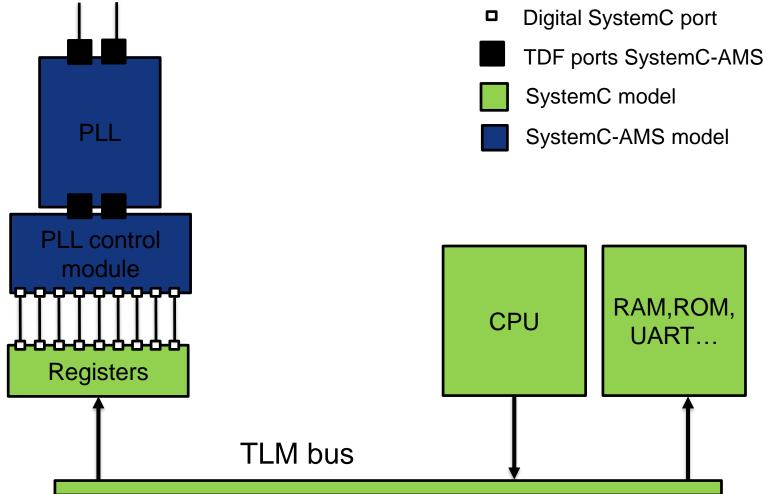

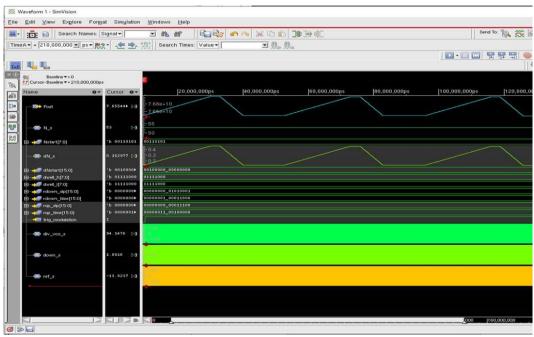

#### SYSTEMC PLL CONTROL WITH REGISTER INTERFACE CONTROL OF A PLL CHIRP GENERATION WITH SOFTWARE AND ARM FASTMODEL . INTEGRATION IN CADENCE XCELIUM / SIMVISION

- PLL contains behavior implemented in TDF

- PLL control module : input SystemC ports, output TDF control for PLL module

- CPU subsystem including ARM model and peripherals (e.g. timer, interrupt controller, etc.)

- Bus infrastructure for communication between CPU subsystem and PLL (TLM)

NP

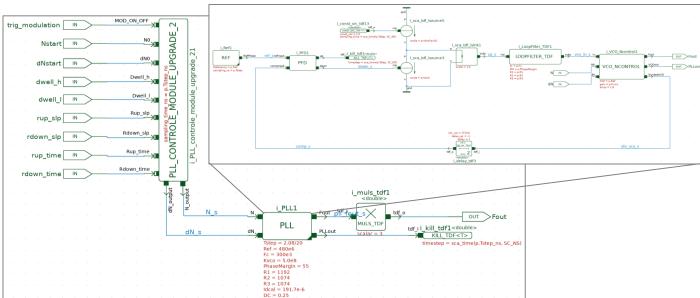

#### PLL IN RADAR TRANSCEIVER

PLL contains behavior implemented in TDF

### Tools and libraries:

SystemIntegrator / Magillem ARM Fastmodels COSIDE Cadence Xcelium

| <pre>#include "tmvhChip_CC_Base.h" #include "tmvhTlm_pll_regs_Reg.h"</pre>                                                                                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                |  |

| <pre>int main(void) {</pre>                                                                                                                                                                                    |  |

| <pre>// set registers // trigger modulation (on) rtiGen_RegisterFieldWrite(TMVH_BASEADDRESS_U_PLL_REGS, TMVH_TLM_PLL_REGS_TRIG_MODULATION_OFFSET, TMVH_TLM_PLL_REGS_TRIG_MODULATION_TRIG_START_MSK, 1 );</pre> |  |

|                                                                                                                                                                                                                |  |

| // wait 200us<br>rtiTim_Sleep(TMVH_BASEADDRESS_U_TIM, rtiGen_us, 200);                                                                                                                                         |  |

|                                                                                                                                                                                                                |  |

| <pre>// End simulation rtiTim_EndSim(TMVH_BASEADDRESS_U_TIM);</pre>                                                                                                                                            |  |

| return 0;<br>}                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                |  |

Control software running on ARM

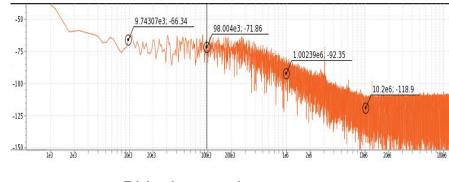

PLL phase noise

Visualization of signals with SimVision

## Conclusion

#### PUBLIC

#### COMPARISON SYSTEMC/AMS VS ADS PTOLEMY

- Goal : Get a fair time comparison between tools

- Same sampling frequency, same simulation time, same cpu (2 proc xeon 2.4G, 16Gram)

|                                        | PLL 35us sim time w/<br>noise (Fs=10GHz) | RXBIST+RX (1ms of<br>sim) Fs=3GHz |

|----------------------------------------|------------------------------------------|-----------------------------------|

| ADS(Ptolemy)                           | 430s                                     | 14 min                            |

| SystemC<br>(before time optimization*) | 119s                                     | 4 min                             |

\* Further increase in simulation speed expected:

- Sampling frequency and timestep can be optimized along the chain, multi-rate system modeling supported

- COSIDE tool offers "profiling" capability to identify where the computation is high, enabling making local optimizations

#### CONCLUSION

- It is possible to simulate RF front end model with high accuracy (UPN, non linearity, ADC oversampling, PLL frac-N chirp generations) and validate specifications and architecture concepts

- The loops, calibrations can be easily simulated using a system-level model: BIST processing can be validated before receiving samples

- The COSIDE environment offers a "friendly user interface" for system modeling in SystemC and SystemC-AMS

However a specific expertise is necessary to create your own models in C++ coding + RF system

- The simulation times remain acceptable and models can be reused in different platforms (matlab, Cadence,...)

- Simulation with processor models (e.g. ARM) is possible and allow software validation before receiving silicon

- Opens the door to extended use of the platform (e.g. pre-validation, pre-verification, ...)

### SECURE CONNECTIONS FOR A SMARTER WORLD