# ANALOG IP – WITH INTELLIGENT IP FROM SYSTEM TO SILICON

Torsten Reich, Fraunhofer IIS/EAS

## Analog IP – with Intelligent IP from system to silicon

#### What is Intelligent IP (on silicon level) ?

- Intelligent IP bottom-up: from silicon to system level

- Intelligent IP top-down: from system level to silicon

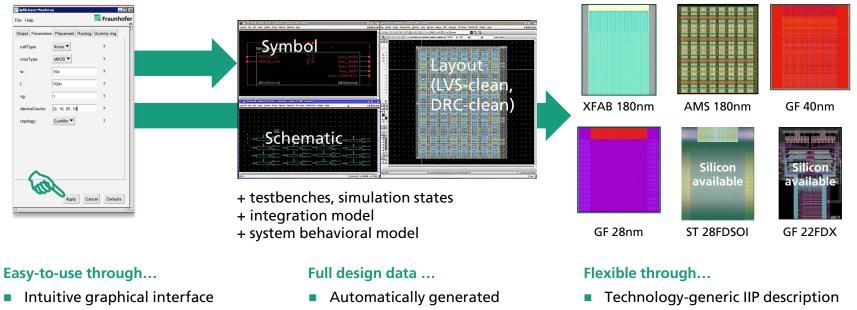

### Our VISION Intelligent A/MS IP (IIP)

#### Offering innovative A/MS IP which are

- flexible as software, processors, memory compilers or soft IP

- configurable by a wide range of different parameters

- generated in a few seconds to minutes

- verified on different technologies in a strictly standardized way

## Intelligent IP A novel approach for analog and mixed-signal IP

Seamless design tool integration

Can be altered "as usual" (non-proprietary)

Automated configuration

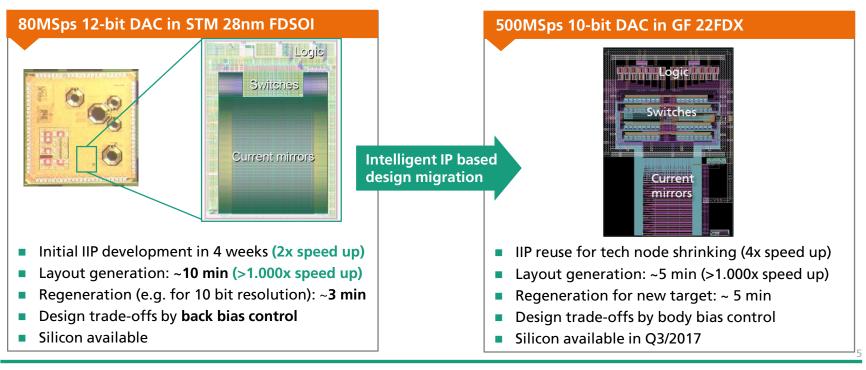

## Intelligent IP Productive application examples & benefits

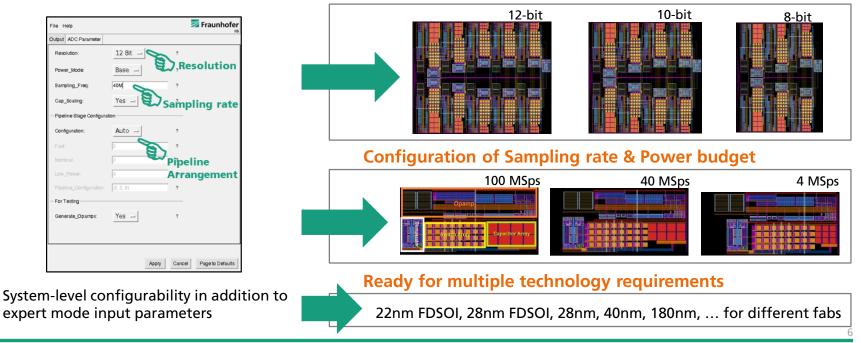

## Intelligent IP Use case Configurability for new product requirements

| Output ADC Parameter   Resolution: 12 Bit   Power_Mode: Base   Sampling_Freq: 40M   -Popeline Stage Configuration ?   Configuration: Auto   -Pipeline Stage Configuration ?   Configuration: Auto   Past: ?   Pipeline Pipeline   Low_Forwer: 6   Proteine_Configuration: ?   Proteine Atrangement   Proteine_Configuration: ? | File Help               |           |          |        | 🖉 Fraunh   | ofer   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|----------|--------|------------|--------|

| Power_Mode: Base - , Resolution<br>sampling_Freq 40M ?<br>Cap_Scaling: Yes Sampling rate<br>-Pipeline Stage Configuration<br>Configuration: Auto - ?<br>Fast Pipeline<br>Low_Power: 0 Arrangement<br>Pipeline_Configuration: (2.2.6) ?                                                                                         | Output ADC Parameter    |           |          |        |            |        |

| Sameling_Free; 40M ?<br>Cap_Scaling: Yes Sampling rate<br>Produce Stage Configuration<br>Configuration: Auto ?<br>Fast: 2<br>Normal: 2<br>Phipeline<br>Low_Power: 9<br>Arrangement<br>Pholine_Configuration: (2.2.6) ?                                                                                                         | Resolution:             | 12 Bit 🖃  | Sol      | ?      |            |        |

| Cap_Scaling: Yes Sampling rate<br>Pipeline Stage Configuration<br>Configuration: Auto ?<br>Fast: 2 ?<br>Nominal: 2 Propeline<br>Low_Power: 0 Arrangement<br>Pipeline_Configuration: (2.2.6) ?                                                                                                                                  | Power_Mode:             | Base -    | E.       | ),Re   | soluti     | on     |

| Configuration: Auto - ?<br>Fast 2 ?<br>Nominal 2 Pripeline<br>Low_Power: 6 Arrangement<br>Ppeline_Configuration: (2,2,6) ?                                                                                                                                                                                                     | Sampling_Freq:          |           | _        | ?      |            |        |

| Configuration: Auto - ?<br>Fast 2 ?<br>Nominal 2 Pipeline<br>Low_Power: 0 Arrangement<br>Pipeline_Configuration: (2.2.6) ?                                                                                                                                                                                                     | Cap_Scaling:            | Yes -     | $D_{Si}$ | a'np   | ling r     | ate    |

| Fast 2   Pripeline   Low_Power:   0   Attrangement   Pipeline_Configuration:   (2,2,0)                                                                                                                                                                                                                                         | Pipeline Stage Configur | ation     |          | - 1    |            |        |

| Nominat 2 Pipeline<br>Low_Power: 0 Arrangement<br>Pipeline_Configuration: (2.2.6) ?                                                                                                                                                                                                                                            | Configuration:          | Auto -    |          | ?      |            |        |

| Low_Power:     0     Arrangement       Pipeline_Configuration:     [2, 2, 6]     ?                                                                                                                                                                                                                                             | Fast                    | 2         | 3        | ?      |            |        |

| Low_Power:     0     Arrangement       Pipeline_Configuration:     (2, 2, 0)     ?                                                                                                                                                                                                                                             | Nominal:                | 2         | er b     | Pipel  | ine        |        |

|                                                                                                                                                                                                                                                                                                                                | Low_Power:              | 8         |          |        |            | ent    |

| - For Testing                                                                                                                                                                                                                                                                                                                  | Pipeline_Configuration: | (2, 2, 6) | _        | ?      |            |        |

|                                                                                                                                                                                                                                                                                                                                | For Testing             |           |          |        |            |        |

| Generate_Opamps: Yes - ?                                                                                                                                                                                                                                                                                                       | Generate_Opamps:        | Yes -     |          | ?      |            |        |

|                                                                                                                                                                                                                                                                                                                                |                         |           |          |        |            |        |

|                                                                                                                                                                                                                                                                                                                                |                         |           | Apply    | Cancel | Page to De | faults |

expert mode input parameters

**Configuration of ADC resolution & Pipeline arrangement**

#### Intelligent IP **Flexible to Electrical Requirements**

Intelligent IP supports electrical requirement flexibility on different levels:

**Primitive level** Design parameter, primitive change, ...

**Functional level** Bandwidth, gain, ...

System level INL, ENOB, resolution...

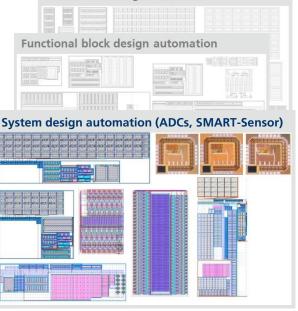

#### **Basic block design automation**

## Analog IP – with Intelligent IP from system to silicon

What is Intelligent IP (on silicon level) ?

#### Intelligent IP bottom-up: from silicon to system level

Intelligent IP top-down: from system level to silicon

## Intelligent IP bottom-up: from silicon to system

## Analog IP – with Intelligent IP from system to silicon

- What is Intelligent IP (on silicon level) ?

- Intelligent IP bottom-up: from silicon to system level

- Intelligent IP top-down: from system level to silicon

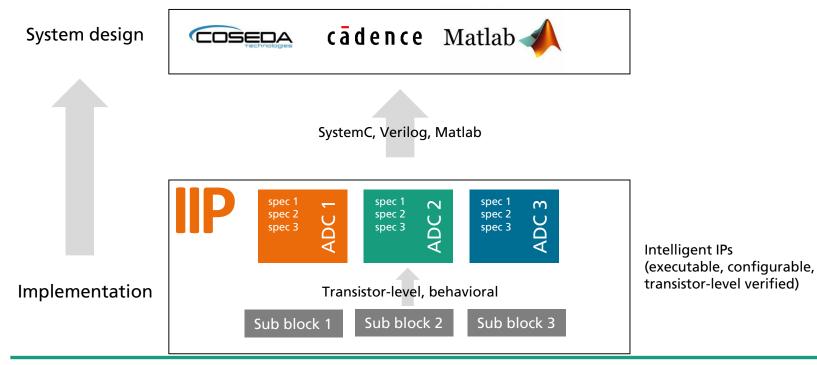

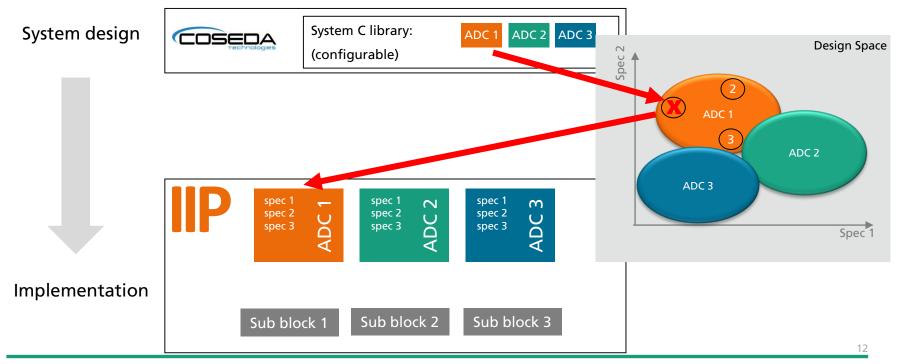

### Intelligent IP top-down: from system to silicon (1)

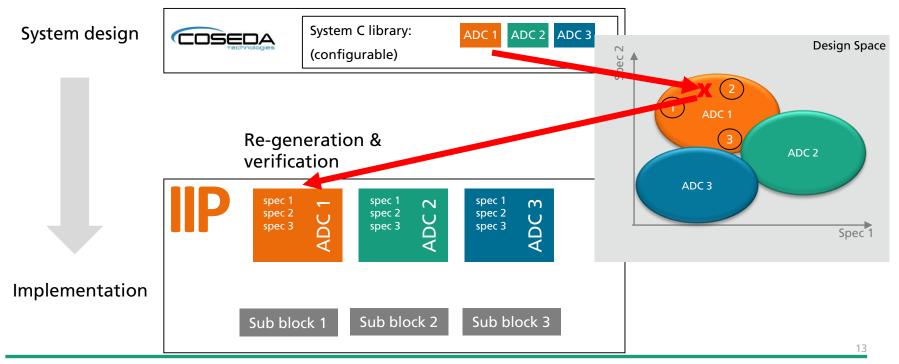

## Intelligent IP top-down: from system to silicon (2)

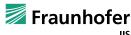

## Intelligent IP top-down: from system to silicon (3)

## Analog IP – with Intelligent IP from system to silicon Conclusion

- Intelligent IP provides automated design of analog IPs & is in productive use

- Generation of system models in development

- Goal: provide configurable SystemC model library in Coside for

- exiting verified A/MS-IPs

- A/MS-IPs, which can be re-generated and verified quickly

- A/MS-IPs, which can be quickly designed using Intelligent IP technology

- Request: discussion on customer problems and expectations

15

#### **INTELLIGENT IP Your Contact**

Dr. Torsten Reich Fraunhofer IIS/EAS

⊠ Torsten.Reich@eas.iis.fraunhofer.de +49 351 4640-761

www.intelligent-ip.org

16