# Fast Virtual Platforms for Scalable Software Verification

Lukas Jünger, MachineWare GmbH lukas@mwa.re

#### $\equiv CARSCOOPS$ •

#### RECALL

#### Mercedes Recalls EQS And EQE EVs For Software Bug That Could Cause Sudden Power Loss

Mercedes must recall 8,281 EQ models as a result of a software glitch that has led two vehicles to lost

motor

Q USA/GLOBAL >

Home > Audi > News

VW Group CEO Admits Audi Lags Behind Rivals, Software Issues To Blame

The automaker wants to speed up EV development.

#### TECH / TRANSPO / CARS

The Verge /

Q

VW's first mass-market EV suffers delay thanks to software struggles / Versions of the ID 3 will now ship in September with unfinished software

Tech / Reviews

Science

Entertainment

####

ne, t Home > Automakers

#### May 11, 2023 09:15 AM

### Volvo, Polestar delay flagship electric SUVs on software issues

Volvo CEO Jim Rowan blames "lumps and bumps" associated with rigorous testing of "mission critical software."

## Motivation

- Software challenges

- Complexity is rising

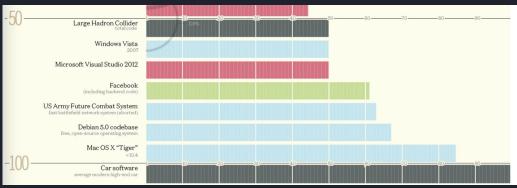

- Car: >100 Mio. lines of code

- Security & safety critical

- Quality is key

https://informationisbeautiful.net/visualizations/million-lines-of-code/

- Bad software is dangerous and expensive

- Accidents, recalls, liability for hacks, maintenance

- Problem: Testing is

- $\circ$   $\,$   $\,$  Hard to automate, hard to scale, limited by hardware resources  $\,$

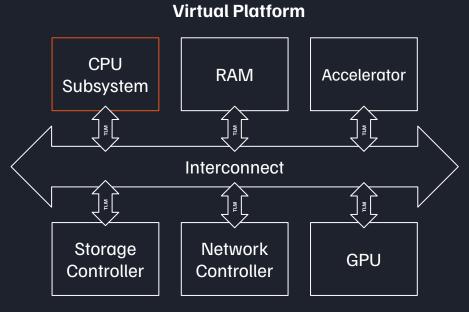

## **Virtual Prototyping**

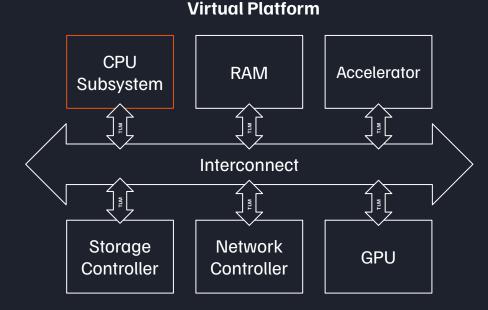

- Virtual Platform: Full System Simulation

- Indispensable in software development

- Everising SW and HW complexity

- Advantages over physical prototypes

- Available earlier (shift-left methodology)

- Full flexibility, deep introspection

- Non-intrusive debug

- Scalability

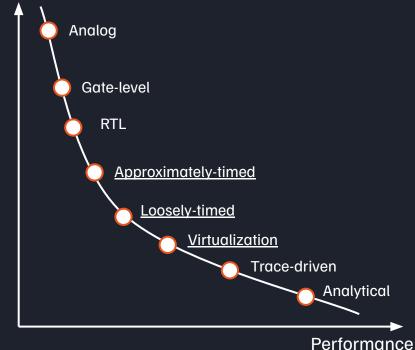

## **Simulation Abstraction Levels and Use Cases**

- Many different techniques available

- No silver bullets

- Right tool for the right job

#### Transaction Level Modeling (<u>TLM</u>):

- Approximately-timed

- Architecture exploration, interconnect

- Loosely-timed

- $\circ$  ~ Early SW development & verification

- Virtualization

- Regression, SW development

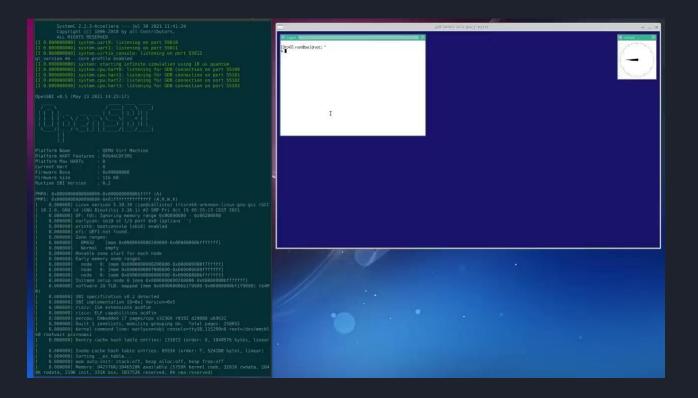

#### Demo

## How to build a fast Simulator (for SW verification)?

- CPU model executes software

- Performance dominates VP

Use Case: Early SW development

- Pre-silicon, No HW available

- Fast SW models required

Use Case: Regression Testing

- HW available, but limited scalability

- HW acceleration possible

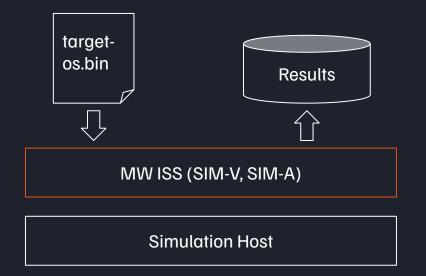

#### **MachineWare Instruction Set Simulators**

- Fast, functional simulators

- SW development and verification

- Architecture exploration

- Shift-left: Better software earlier

- Easy to use and integrate

- Intuitive API and user interface

- Well documented

- Bring your own environment

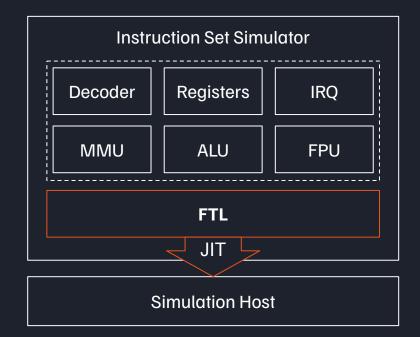

## **Fast Translator Library**

- Processor Modeling Toolkit

- Model your processor in C++

- Partially automated modeling flow

- Fast JIT binary translation

- No target software limitations

- Custom instrumentation

- Custom extensions

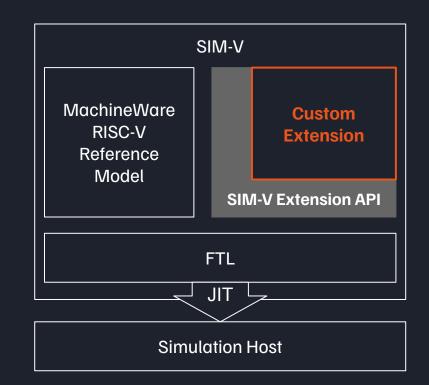

#### **SIM-V Custom Extensions**

- Customization is a RISC-V USP

- Add custom instructions, registers, CSRs, ...

- **SDK** for extensions development

- No modifications to SIM-V

- Extension automatically loaded

- Easy to use

- Leverage FTL for performance

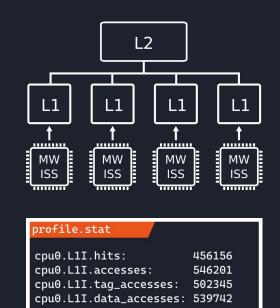

#### **FTL Observer Cache Models**

- Instrument memory transactions

- Cache receives addresses

and maintenance operations

- Analyze statistics

- Numerous statistics allow to asses cache and application performance

- Model custom cache hierarchies

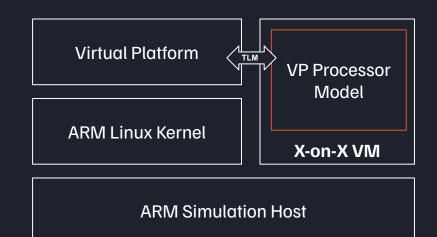

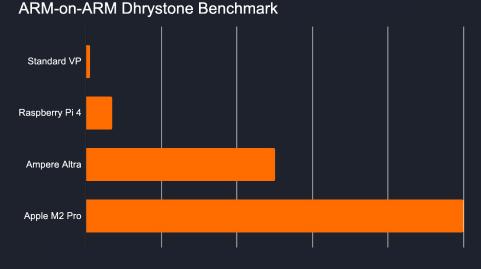

#### **ARM-on-ARM**

- Traditionally X-on-Y (e.g. ARM on X86)

- Unavoidable ISS overhead ~5-10x

- No 1-1 instruction mapping

- In-memory processor state

How about X-on-X?

- Encapsulate processor model in VM

- Regular TLM-based VP

- ~80% of native performance

#### **ARM-on-ARM Dhrystone Benchmark**

- Dhrystone benchmark measures numeric compute performance

- Upper performance bound

- On good hardware significant boost

- Limited to host HW

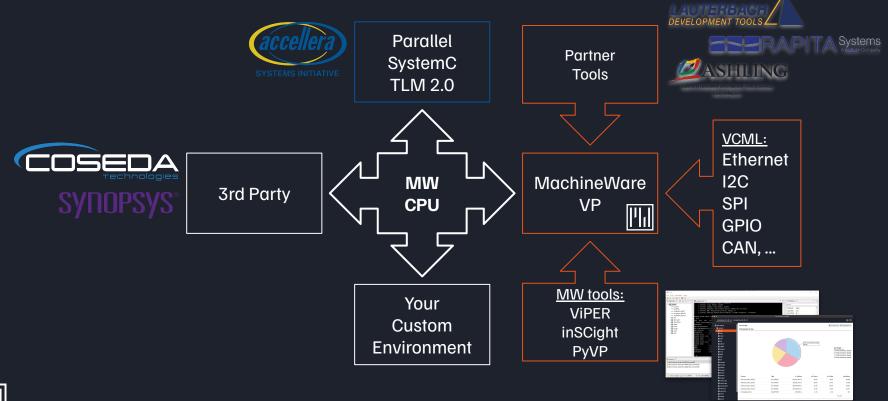

## Interoperability

#### **Partners**

LAUTERBACH DEVELOPMENT TOOLS

Experts in Embedded Development Tools & Services

www.ashling.cor

Technologies

#### Summary

- CPU models are key for SW verification

- Fast, parallel ISS required

- Model interoperability important

- Good starting point: SystemC TLM-2.0

- Host HW acceleration promising

- Utilize host processor, GPU, ...

- No silver bullets

## Thanks!

Questions?