# Firmware bring-up and integration on SystemC VP with COSIDE

COSEDA User Group Meeting 2022

Ana-Maria Plaiseanu(IFRO DCBUC ATV SC D DD)

- restricted -

#### Agenda

- > Background and motivation

- > Workflow

- Block diagram

- Concept feasibility VP development

- Firmware integration

- Testing concept

- Regression results

- Benefits

- First step design SystemC virtual prototype with a Python backend for concept feasibility

- Performance-driven architectural choices during early chip concept stage

- > Next step refinement of model used in concept feasibility for design team

- Supports building the design from bottom up high complexity systems split into smaller, more manageable pieces (modules)

#### Motivation of FW developer

- > High complexity bugs hide at the 'edges' of the design

- Interaction between firmware units

- Interaction between firmware and hardware

- > Firmware and digital design activities are not necessarily synchronized

- Effort of verification increases late in design phase FW and HW activities are done

- Simulation time is slow for Firmware necessities (gate level not necessary for SW)

- > FW on top approach shifts integration verification effort to FW team

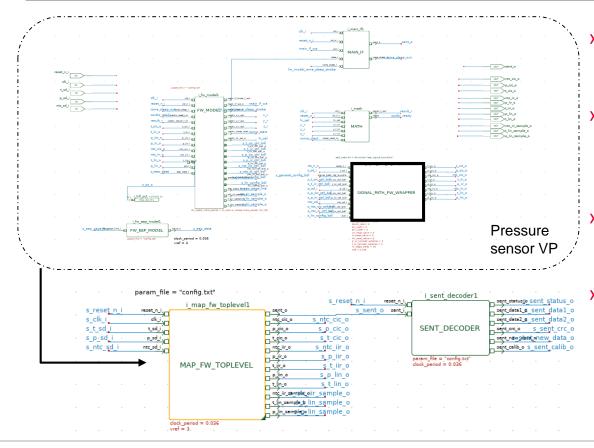

### Block diagram – Manifold air pressure application

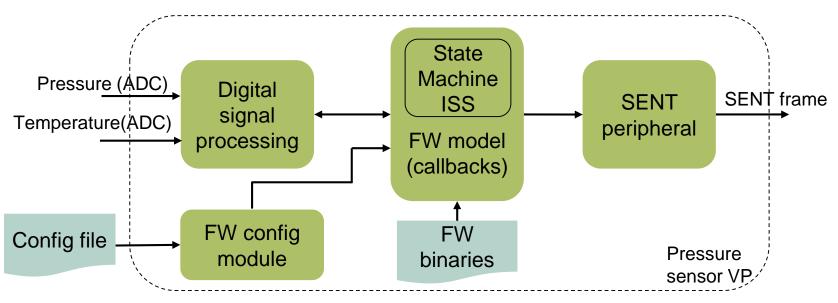

## Concept feasibility VP development

- Digital core VP driven by concept requirements

- Model implements digital core of a pressure sensor used for manifold application

- During concept feasibility – only digital signal processing path was of interest

Copyright © Infineon Technologies AG 2020. All rights reserved.

#### Firmware integration

- > Integration of further level of detail and 'peripherals' used by FW as SC modules

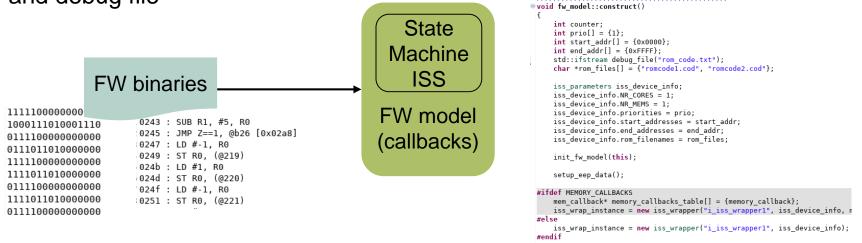

- Integration of state machine core instruction set simulator

- Supports performance parameters evaluation emulating target behaviour -Timing analysis is critical for FW development in small ASICs

- Coupling between ISS and FW code done through sc\_module wrapper implementing FW model callbacks

- Separate callbacks for program counter iteration as well as read/write access to internal registers and RAM

- Firmware code thus integrated as precompiled binaries using specific compiler and debug file

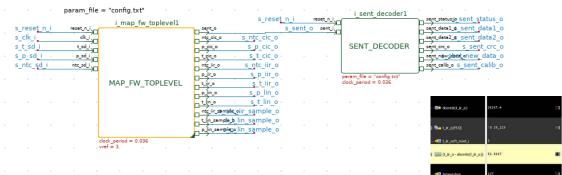

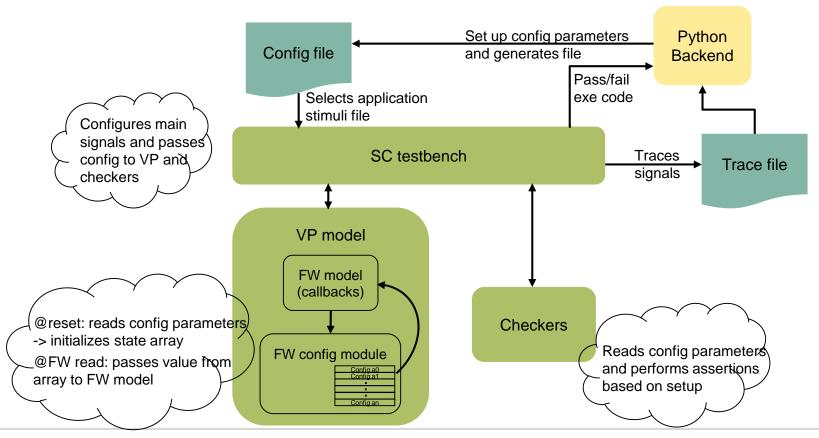

#### Testing concept - General

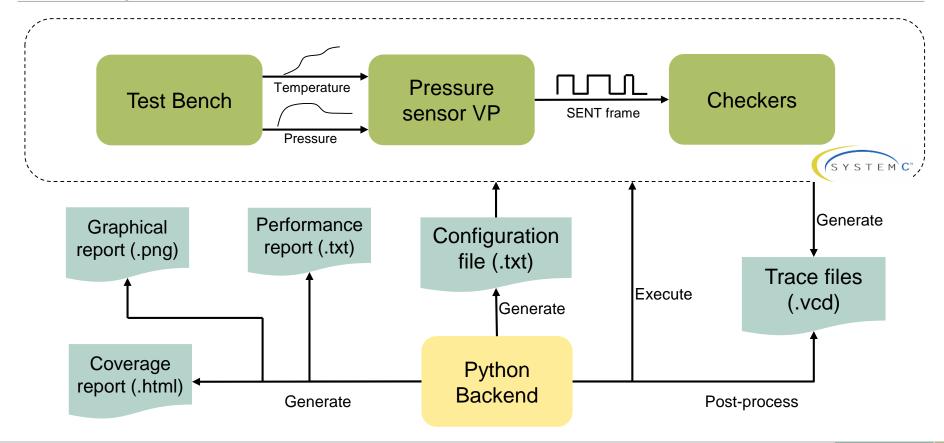

Simple test bench instantiating VP and SENT decoder fulfilling 'checkers' role Stimuli driven programmatically in multiple stimuli files based on application (signal ramp, mid range, signal step etc.) Selection of stimuli done in regression based on implemented test case Rest of VP configuration done through *config.txt* file coupled to model parameters as well as configuration signals in dedicated module

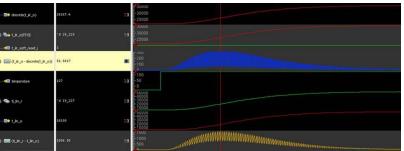

#### Testing concept – simulation and co-simulation

Each stimuli TB setup checked in simulation also co-simulation with Xcellium coupling

|                      |              | Baseline = 0 |            | Timoù - 45 87942 | 2001 ***                                |

|----------------------|--------------|--------------|------------|------------------|-----------------------------------------|

| Name                 | o→ Cursor o→ | - 0  10ms    | 20ms  30ms | 40ms 50          | ns 60ms                                 |

|                      | 440.859      | 26515.6      | 530.487    | 440.859          | 1017.98                                 |

| wiput_state_o        | 1            |              |            |                  |                                         |

| ntc_range_sel_o[2.0] | 'h 1         | 2 (4 ) 5     | (4 )(3 )(2 | 1                | (2                                      |

|                      | 1            | F40000       |            |                  | 65520                                   |

| ⊕-¶an ntc_ir_r       | *a 55_067 ÷⊒ | 1 20000      |            |                  | ••••••••••••••••••••••••••••••••••••••• |

|                      | ·d 1380      |              |            |                  |                                         |

#### Testing concept – from testbench to regression

- Configures the VP, handles and sets up the environment parameters through the configuration file.

- Launches multiple VP simulations in parallel on separate CPU cores or dispatches them on Unix LSF machines.

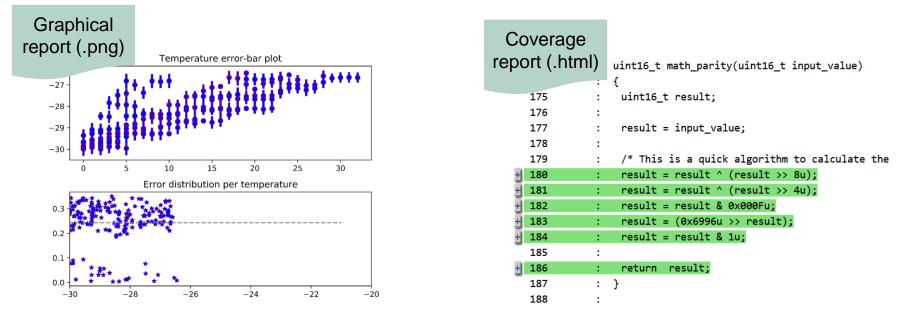

- Handles post-processing of results after simulation runs and supports creation of both tabular and graphical format reports.

- > Enables easy regression runs and automated testing.

### **Regression results**

- > Regressions run on average **32.000** tests dispatching on LSF 50 jobs at a time

- Runtime for one such regression is ~1.5-2 days

- > Performance report extracted with number of fails and configuration files saved for failed tests

- > Graphical reports as well as coverage reports generated

#### **Benefits**

Easily Fast iteration extendable Start FW loops setup to other integration concept2design applications testing early on and once VP is design phase design2design available High reusability Very fast of VP & TB as Reusable for regression well as Python other times with focus backend stakeholders on application between (PreSi Ver) projects

# Part of your life. Part of tomorrow.