Ralph Görgen 28.10.2019

SECURE CONNECTIONS FOR A SMARTER WORLD

Company Public – NXP, the NXP logo, and NXP secure connections for a smarter world are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2019 NXP B.V.

#### Outline

- Motivation: Automotive Battery Safety

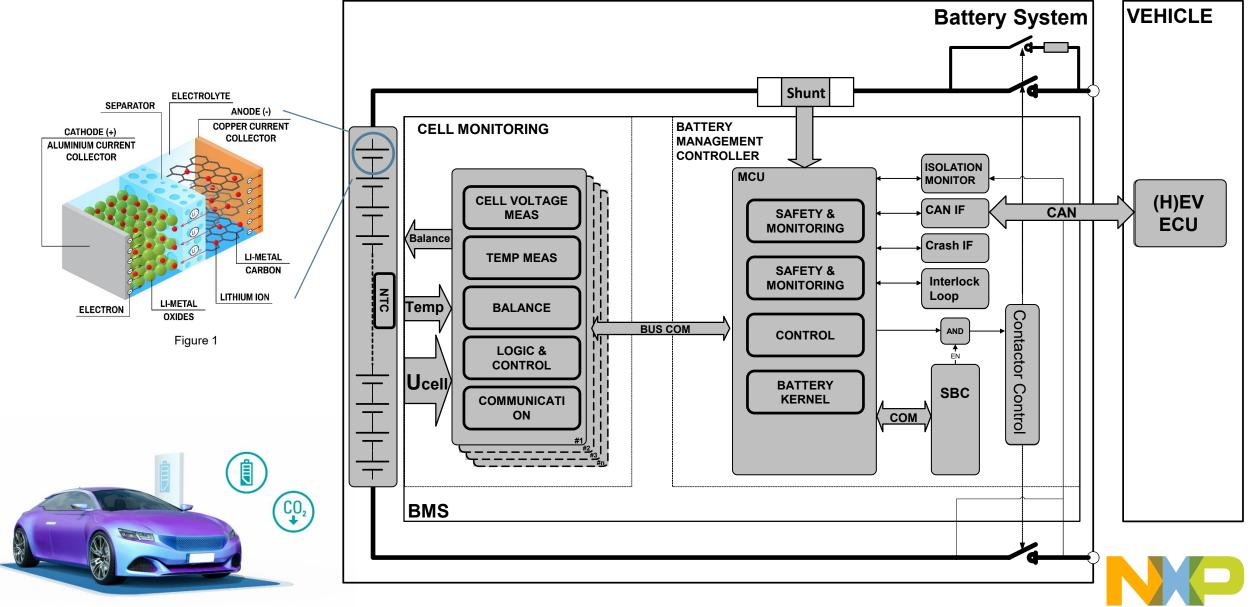

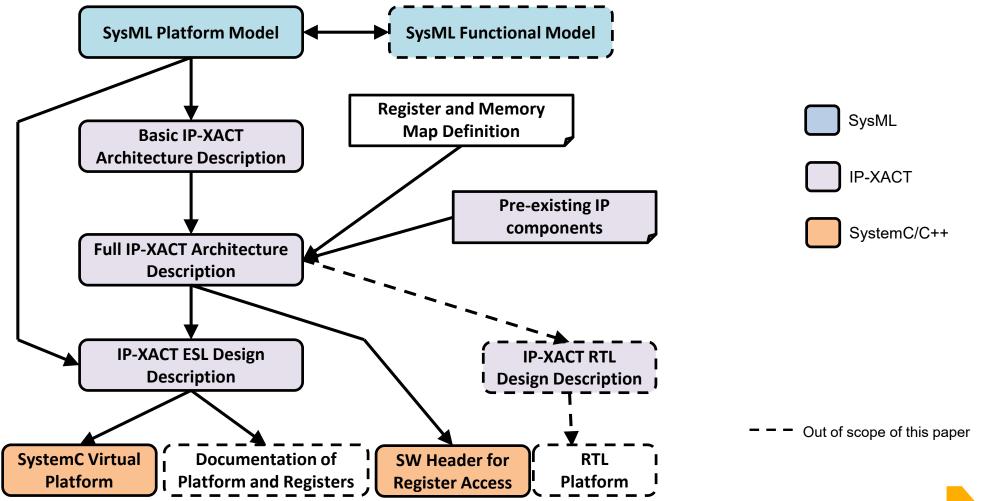

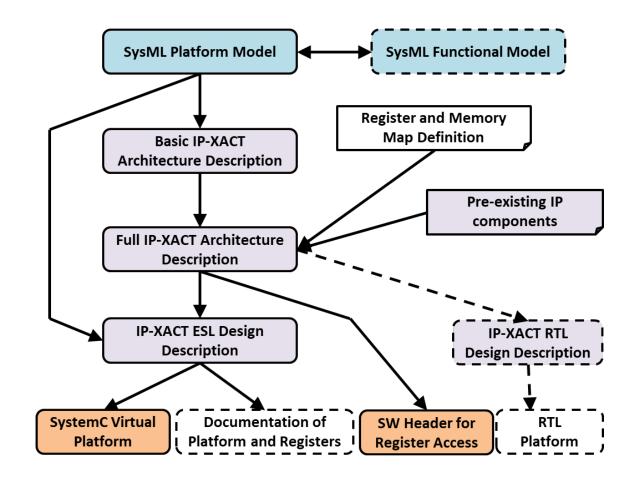

- Model-based Top-Down Flow

- Automated Platform Generation Flow

- Extension to Support AMS

- Summary and Conclusion

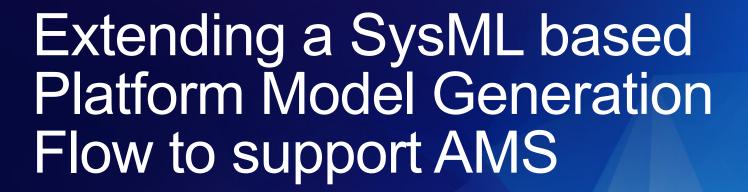

Li-lon traction battery incl. BMS example

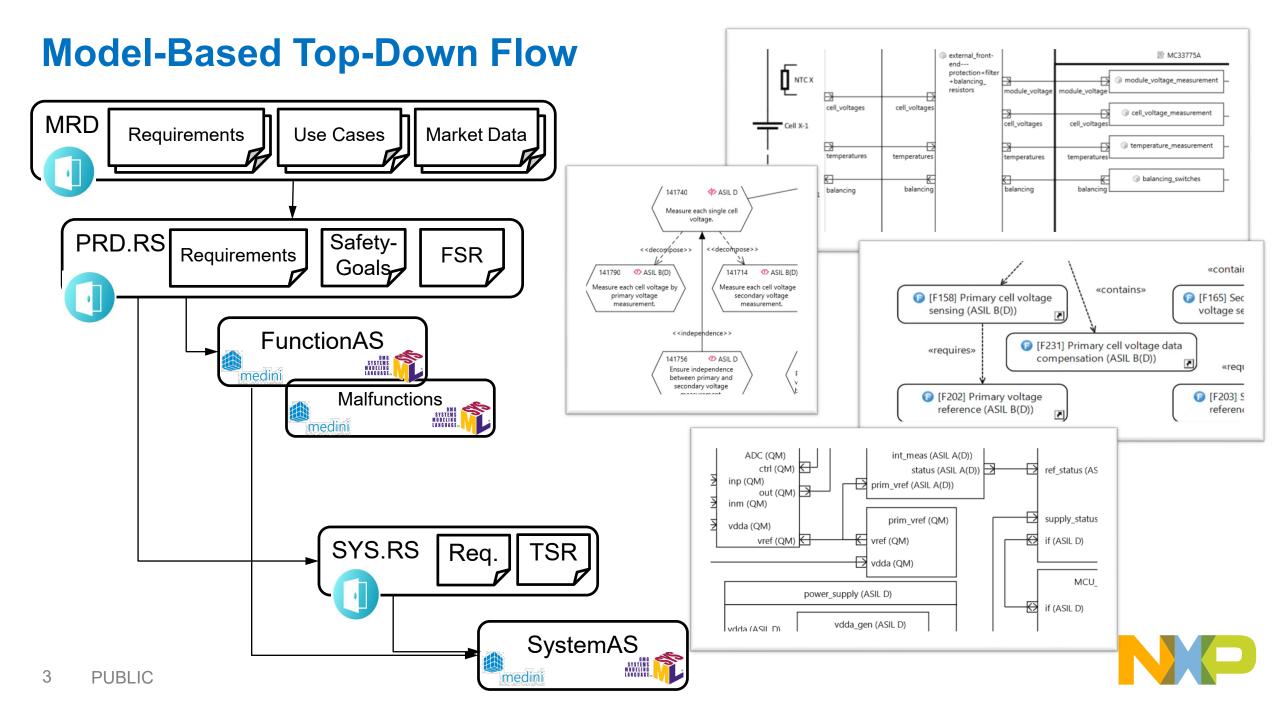

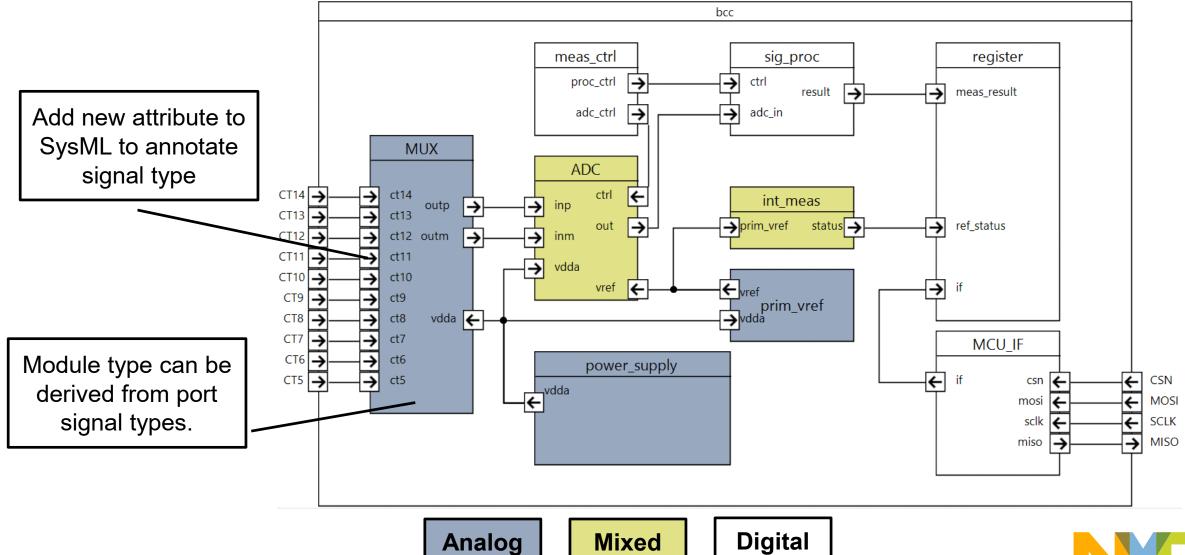

## **Hardware Architecture Model (Platform Model)**

- IC level hardware architecture described in SysML Internal Block Diagram

- Decomposed hardware resources and communication links

#### **Platform Model Generation Flow**

#### **Platform Model Generation Flow (II)**

- Integrated in existing design and system integration framework

- Design tools

- Directory structures

- Documentation rules

**-** . . .

All extensions need to fit in this framework

#### **AMS Extensions for IP-XACT**

- Accellera Vendor Extensions for Analog and Mixed Signal

- Will become native element in next version of IP-XACT standard (IEEE 1685-202x)

- Extends IP-XACT wire port

- domainTypeDefs

- Describes domain type of a port per view, e.g. electrical

- signalTypeDefs

- Describes the signal semantics of a port per view

| signalType                  | Verilog AMS      | SystemC AMS                              |

|-----------------------------|------------------|------------------------------------------|

| continuous conservative     | electrical outp; | sca_eln::sca_terminal outp;              |

| continuous non-conservative | sf_voltage outp; | sca_lsf::sca_out outp;                   |

| discrete                    | wreal outp;      | sca_tdf::sca_out <double> outp;</double> |

#### **Annotate AMS Attributes in Platform Model**

#### **Generation of IP-XACT Description**

```

nxp::createComponent nxp.com bms bcc ADC 2.0 ${nxp::workarea}/chip lib/bcc ADC/METADATA/

nxp::createWirePort inp pi in ""

nxp::createWireTypeDefs inp pi [ list kms::analog [ list ESL ] false [ list analog.h ] ]

4

nxp::createWirePort inm pi in ""

nxp::createWireTypeDefs inm pi [ list bms::analog [ list ESL ] false [ list analog.h ] ]

6

nxp::createWirePort vdda pi in ""

nxp::createWireTypeDefs vdda pi [ list bms::analog [ list ESL ] false [ list analog.h ] ]

8

nxp::createFileSet ESL \

9

[ list \

10

[ list ADClib \

[ list \

11

Create component

../coside/lib/bcc ADC.h \

../coside/lib/bcc ADC.cpp ]\

13

Create ports

14

1\

15

Create fileset

16

nxp::generateXmlAmsExtension nxp.com bms bcc ADC 2.0 \

17

[ list ] \

18

[ list \

Create port signal types

19

[ list inp pi discrete ESL ] \

[ list inm pi discrete ESL ] \

20

21

[ list vdda pi discrete ESL ] \

22

```

#### **AMS Component in IP-XACT**

```

💸 bcc_ADC [2.0] 🛭

¬ → nxp.com/bms/bcc ADC/2.0

▶ ■ Bus Interfaces

V<sub>k</sub> Views

Wire

▼ Vendor Extensions

▼ V<sub>E</sub> accellera_1:signalTypeDef

¥ accellera_1:signalType

¥ accellera:viewNameRef

Port (inm_pi)

Port (vdda_pi)

Port (vref pi)

Port (ctrl_pi)

Port (out po)

▶ File Sets

```

#### VendorExtensions:

```

<accellera:wire>

<accellera_1:signalTypeDefs>

<accellera_1:signalTypeDef>

<accellera_1:signalType>discrete</accellera_1:signalType>

<accellera:viewNameRef>ESL</accellera:viewNameRef>

</accellera_1:signalTypeDef>

</accellera_1:signalTypeDefs>

</accellera:wire>

```

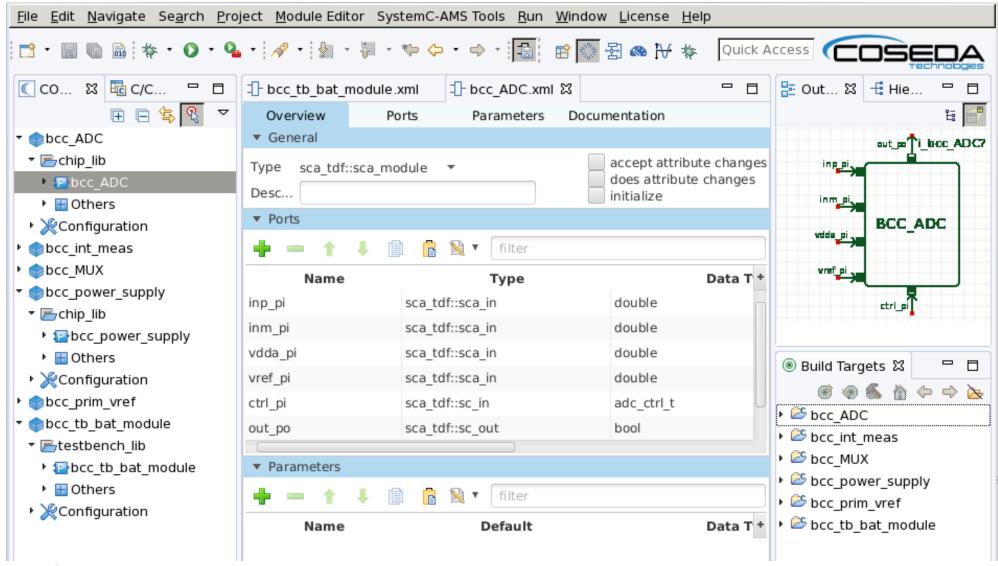

#### **Generate SystemC Model from IP-XACT**

- Digital leaf components

- NXP internal tool generate modules incl. interface and registers

- Register models based on SCML

- Base module for generated elements and derived module to add behavior

- Hierarchical components

- Commercial SystemC Netlister (Magillem tool suite)

- Data types for ports/signals

- Header file containing default typedef to int

- Build files for SystemC compilation based on filesets

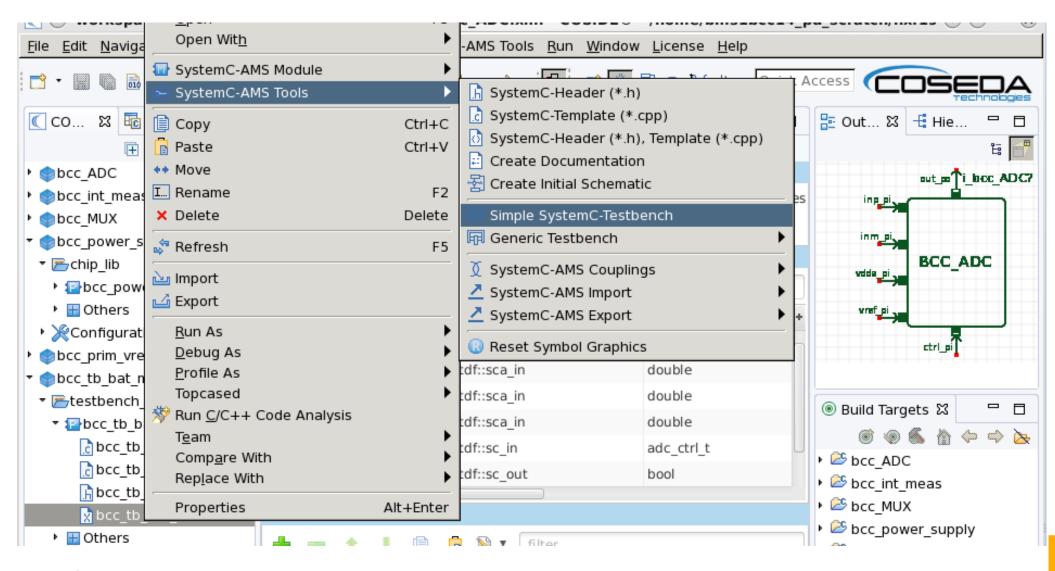

## **Create Analog Components in COSIDE**

#### Starting Point to Implement Component Behavior

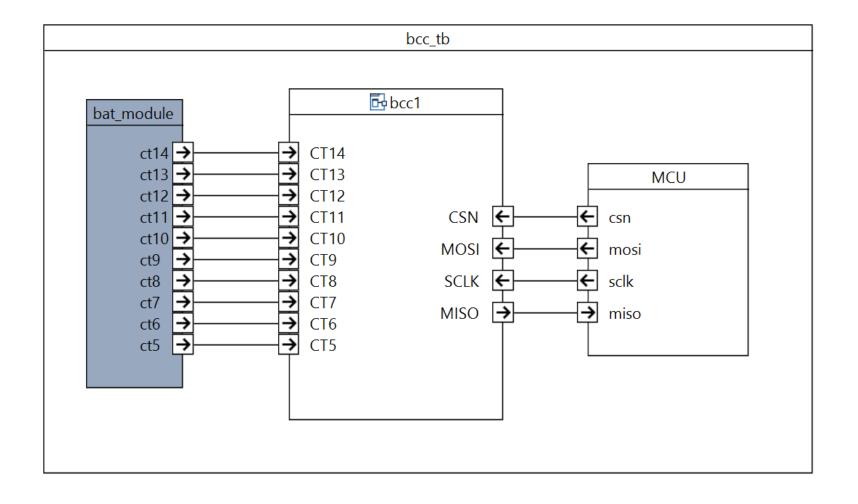

#### **Add Testbench to Complete Model**

#### **Compile and Run Virtual Prototype**

```

File Edit View Scrollback Bookmarks Settings Help

ra/build $ bin/BMS1BCC

SystemC 2.3.1-Accellera --- Nov 6 2018 17:45:13

Copyright (c) 1996-2014 by all Contributors,

ALL RIGHTS RESERVED

SystemC AMS extensions 2.1.0-COSEDA Release date: 20160404

Copyright (c) 2010-2014 by Fraunhofer-Gesellschaft IIS/EAS

Copyright (c) 2015-2016 by COSEDA Technologies GmbH

Licensed under the Apache License, Version 2.0

Info: SystemC-AMS:

6 SystemC-AMS modules instantiated

1 SystemC-AMS views created

6 SystemC-AMS synchronization objects/solvers instantiated

Info: SystemC-AMS:

1 dataflow clusters instantiated

cluster 0:

6 dataflow modules/solver, contains e.g. module: bcc.bat_module

6 elements in schedule list,

1 us cluster period,

ratio to lowest: 1 e.g. module: bcc.bat module

ratio to highest: 1 sample time e.g. module: bcc.bat module

2 connections to SystemC de, 1 connections from SystemC de

```

#### **Summary and Conclusion**

- Model-based top-down flow for safety-critical semiconductor products

- Automated flow to generate skeleton for executable VP form platform model

- Flow extension for AMS based on IP-XACT AMS extensions and COSIDE

#### Conclusion

- Good integration in existing system integration environment

- COSIDE fits well for AMS component modeling and refinement

- Manual creation of projects and modules in COSIDE breaks automation

- Script interface to control basic COSIDE functions would be helpful

## Questions?

Context of this work:

SysML Based Architecture Definition and Platform Generation Flow

DVCon Europe 2019 | Oct 30, 15:15 - 16:45 | Forum 6: System Level Design

# SECURE CONNECTIONS FOR A SMARTER WORLD