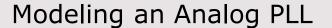

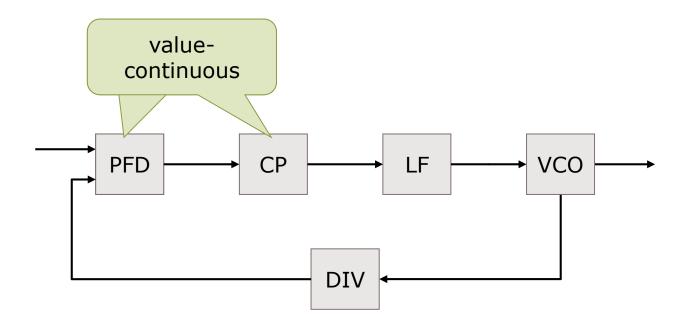

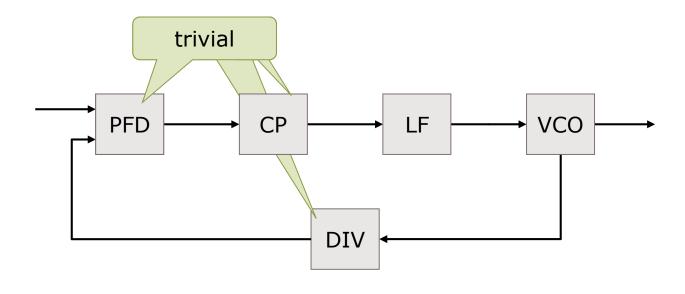

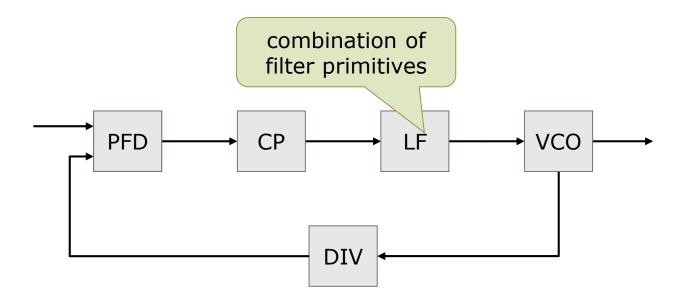

# **Behavioral Modeling for SoC Simulation**Bridging Analog and Firmware Demands

Rainer Findenig

Infineon Technologies

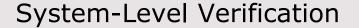

"Set x to achieve optimized y!"

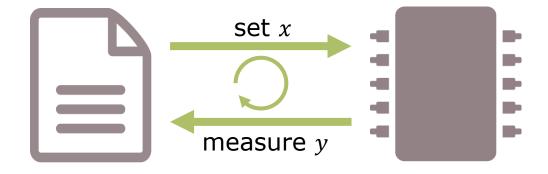

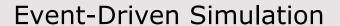

Simulation performance

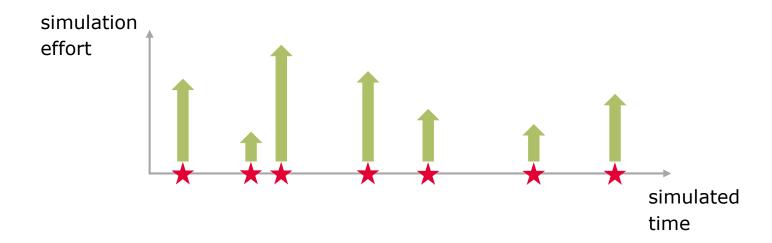

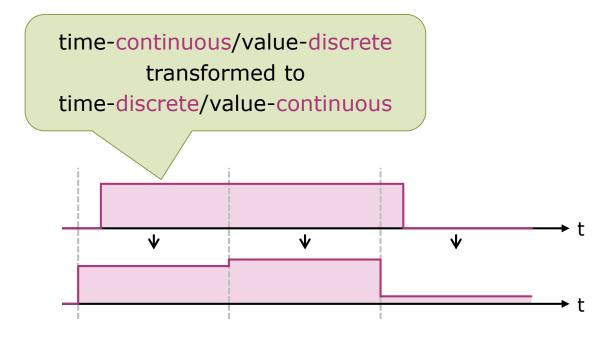

- Unidirectional data flow (real/double)

- Continuous value, discrete time

- No analog solver required

- Event-driven simulator

?

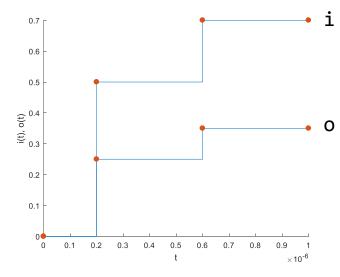

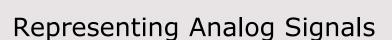

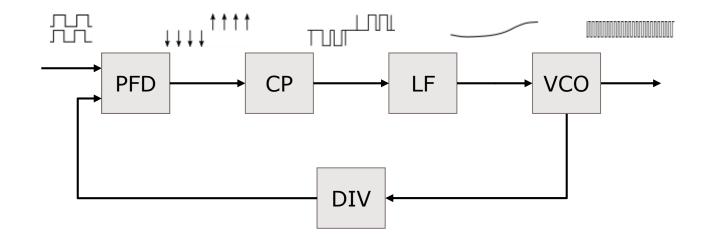

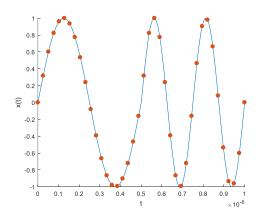

piecewise constant x(t) = a

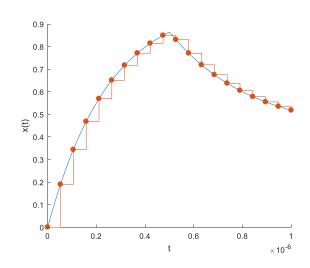

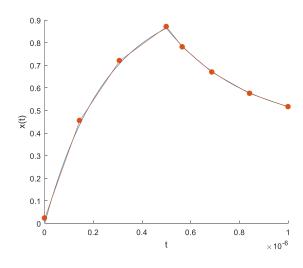

piecewise linear

$$x(t) = a + b(t - t_0)$$

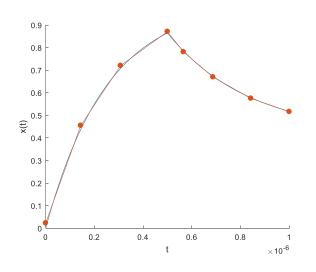

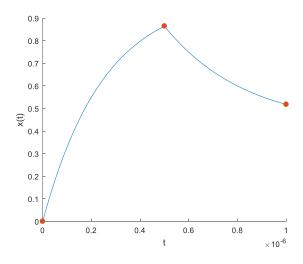

piecewise exponential

$$x(t) = a_0 + \sum_{i} a_i e^{-p_i(t - t_0)}$$

B. C. Lim, J. E. Jang, J. Mao, J. Kim, and M. Horowitz, "Digital Analog Design: Enabling Mixed-Signal System Validation," *IEEE Design Test*, vol. 32, no. 1, pp. 44–52, Feb. 2015.

J. E. Jang, M. J. Park, D. Lee, and J. Kim, "True event-driven simulation of analog/mixed-signal behaviors in SystemVerilog: A decision-feedback equalizing (DFE) receiver example," in *Proceedings of the IEEE 2012 Custom Integrated Circuits Conference*, 2012, pp. 1–4.

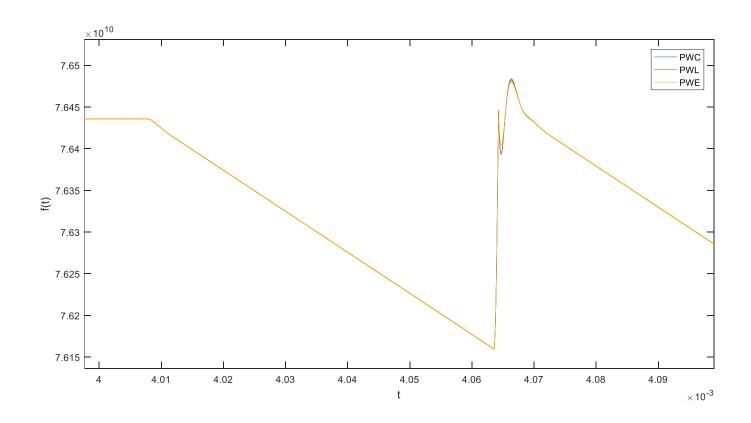

#### Piecewise Constant

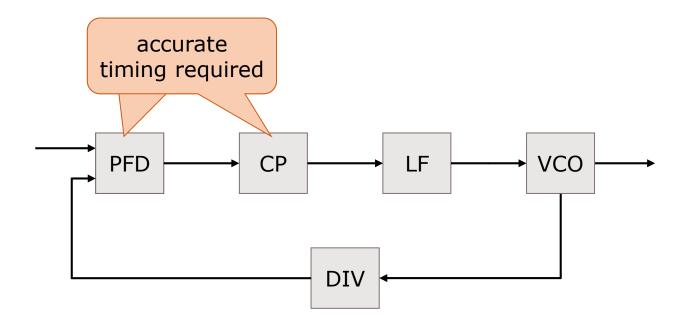

M. H. Perrott, "Fast and accurate behavioral simulation of fractional-N frequency synthesizers and other PLL/DLL circuits," in *Proceedings 2002 Design Automation Conference*, 2002, pp. 498–503.

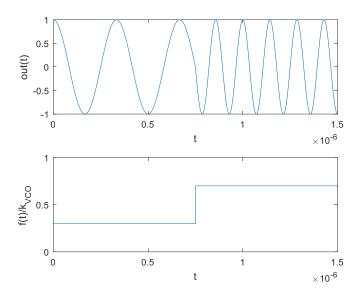

#### Piecewise Constant

- + Easy to model

- + Structure readily obvious

- + Real-number datatypes

– ≥10x oversampling

### Piecewise Linear

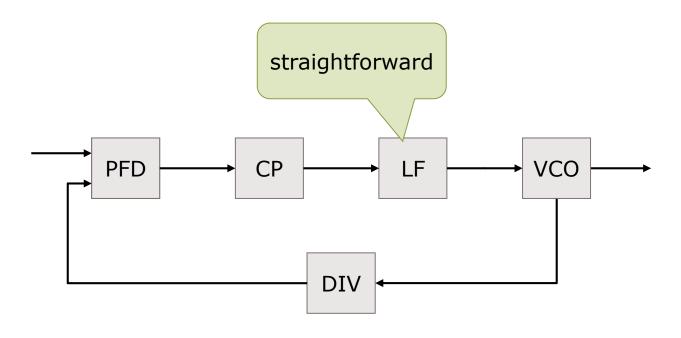

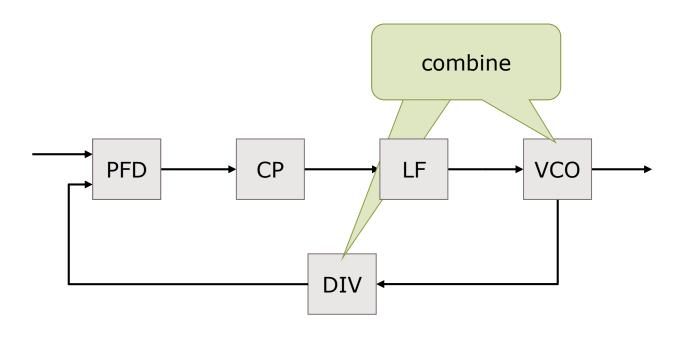

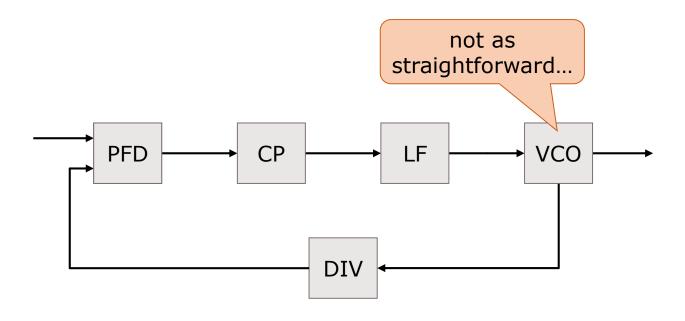

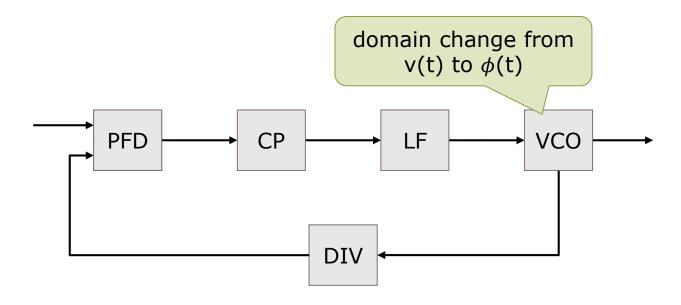

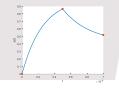

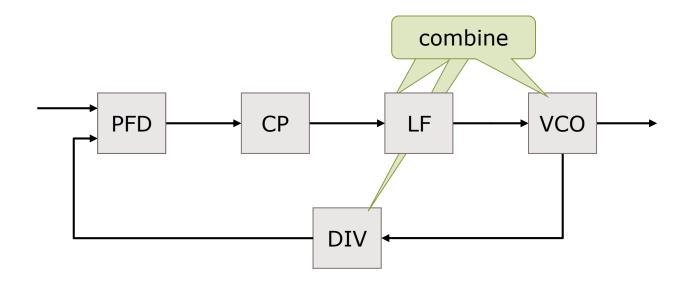

VCO's output is highly nonlinear...

B. C. Lim, J. E. Jang, J. Mao, J. Kim and M. Horowitz, "Digital Analog Design: Enabling Mixed-Signal System Validation," *IEEE Design & Test, vol. 32*, no. 1, pp. 44-52, Feb. 2015.

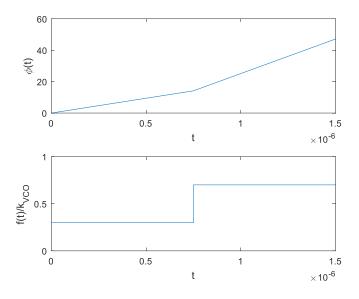

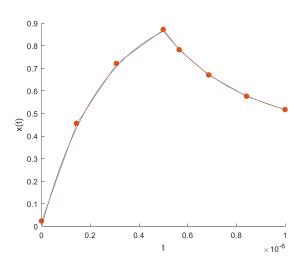

#### Piecewise Linear

...but not when considering the frequency/phase domain!

B. C. Lim, J. E. Jang, J. Mao, J. Kim and M. Horowitz, "Digital Analog Design: Enabling Mixed-Signal System Validation," *IEEE Design & Test, vol. 32*, no. 1, pp. 44-52, Feb. 2015.

#### Piecewise Linear

- + Easy to model

- + Close to original structure

- + Significantly faster

- Three-valued datatypes

- More samples than necessary

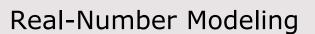

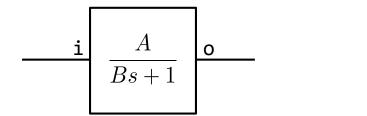

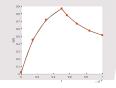

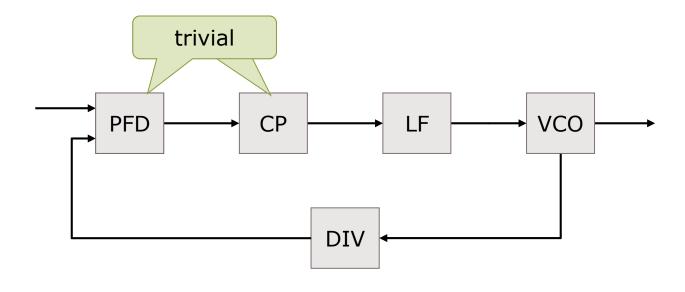

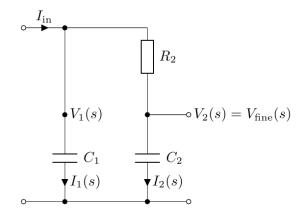

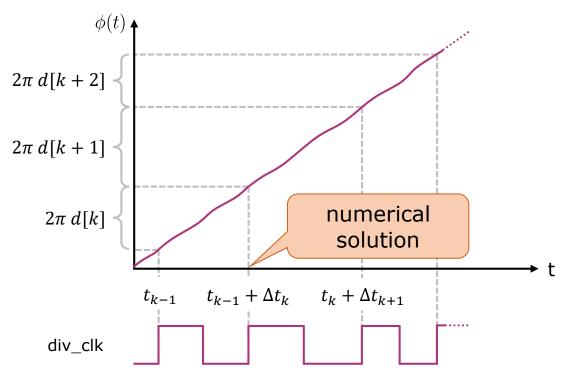

## Piecewise Exponential

$$I_{1}(s) = \dots$$

$$I_{2}(s) = \dots$$

$$V_{2}(s) = \dots = V_{\text{fine}}$$

$$I_{\text{in}}(s) = \sum_{i} I_{i}(s)$$

$$\Phi(s) = 2\pi \frac{f_{0} - k_{\text{vco}} v_{\text{fine}}(0)}{s^{2}} + 2\pi k_{\text{vco}} \frac{V_{\text{fine}}(s)}{s} + \frac{\phi_{0}}{s}$$

$$\downarrow \qquad \qquad \qquad \qquad \qquad \downarrow$$

$$\phi(t) = f\left(v_{0}, \phi_{0}, i_{\text{in}}, f_{0}, k_{\text{vco}}, t\right)$$

M. V. Paemel, "Analysis of a charge-pump PLL: a new model," IEEE Transactions on Communications, vol. 42, no. 7, pp. 2490-2498, Jul. 1994.

M. H. Perrott, M. D. Trott, and C. G. Sodini, "A modeling approach for  $\Sigma$ - $\Delta$  fractional-N frequency synthesizers allowing straightforward noise analysis," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 8, pp. 1028–1038, Aug. 2002.

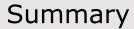

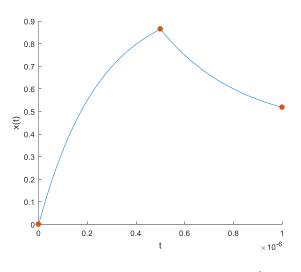

## Piecewise Exponential

- + Minimal number of samples

- Accurate (no approximation in LF)

- + Even faster

- Many-valued datatypes

- Equation set needs to be solved

- Numerical solution

- Loop filter and VCO not separable

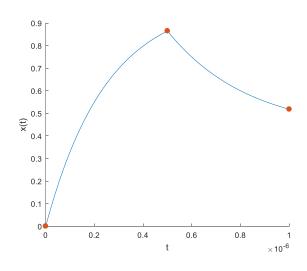

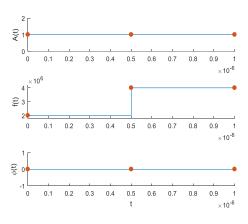

## complex data type: more information, fewer events

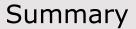

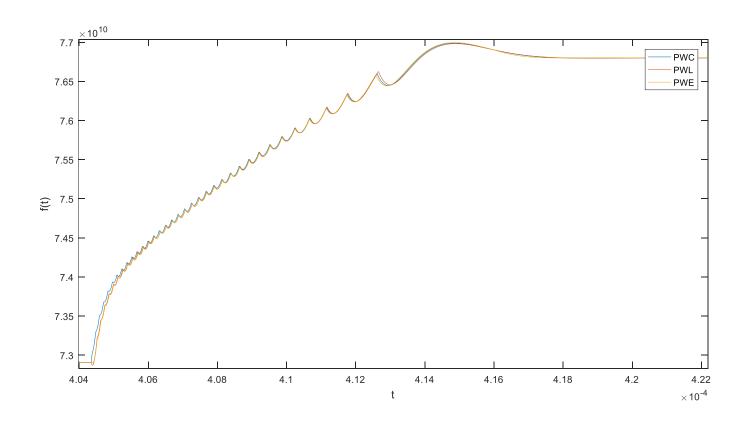

piecewise constant

piecewise linear

piecewise exponential

calculation complexity vs. number of events

- Similar results achieved for a switch-mode power supply system

- Digital IC + external analog components

- Representing continuous-wave signals

Mapping functional models to FPGA/GPU

Part of your life. Part of tomorrow.