# RTL to Software Model using COSIDE<sup>®</sup> and SystemC COSEDA User Group 2022

Ashot Hambardzumyan FPGA Engineer

Nov 24<sup>th</sup>, 2022

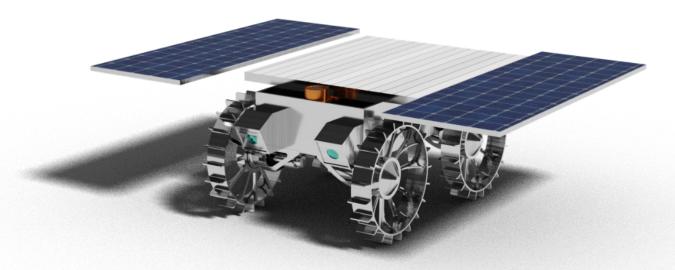

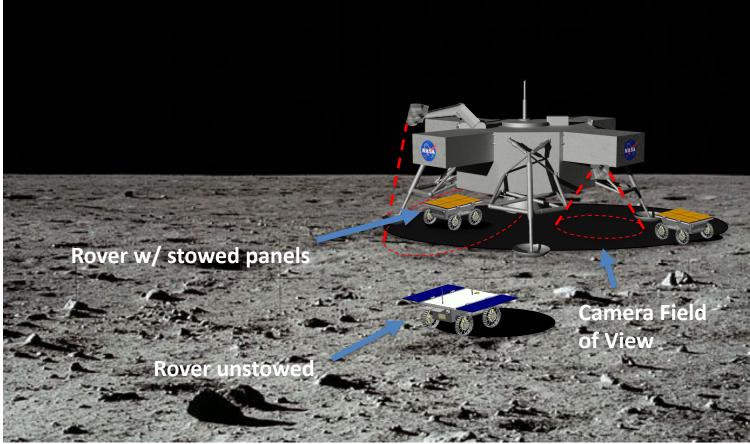

**CADRE:** Cooperative Autonomous Distributed Robotic Exploration

California Institute of Technology

CADRE – Cooperative Autonomous Distributed Robotic Exploration

- 1. CADRE Mission

- 2. CADRE FPGA Architecture

- 3. Current process for SW-HW co-development

- 4. Verilator Support in COSIDE

- 5. Software Modeling using IPC

- 6. Software Modeling using SystemC

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

CADRE is a flight technology demonstration to demonstrate multi-agent cooperative autonomy, performing distributed measurement, on the surface of the moon.

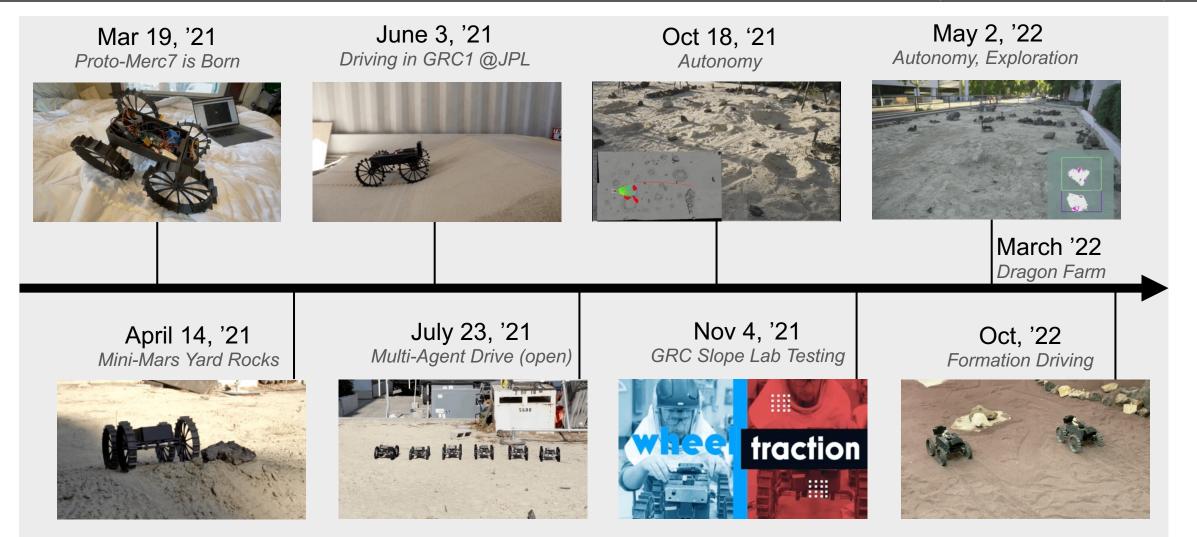

# CADRE Through the Ages

Jet Propulsion Laboratory California Institute of Technology

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

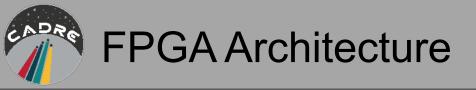

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

#### Features:

- Enforced Power States

- Watchdogs, Runout Timer, Alarm Clock

- Closed-Loop Survival Heater Control

- IMU Driver

- Sun Sensor Driver

- Fault Protection

- Low Power core

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

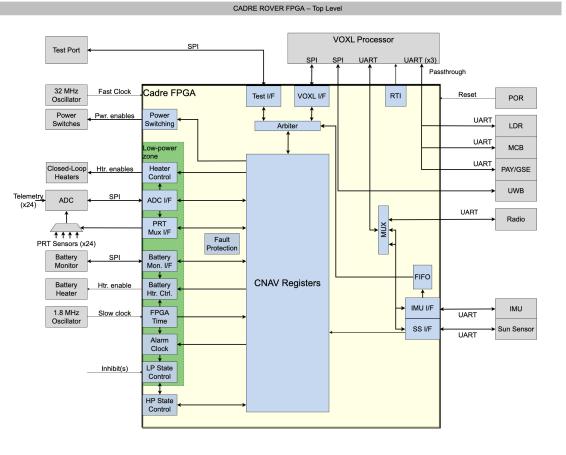

## How FPGA and Flight Software co-development communicate today

Shortcomings:

- Documents come out of sync

- Written description can be interpreted differently

- Software has to build an FPGA model to test with

- Integration bugs won't be found until hardware is ready to run the software.

\_

Jet Propulsion Laboratory California Institute of Technology

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

# Steps:

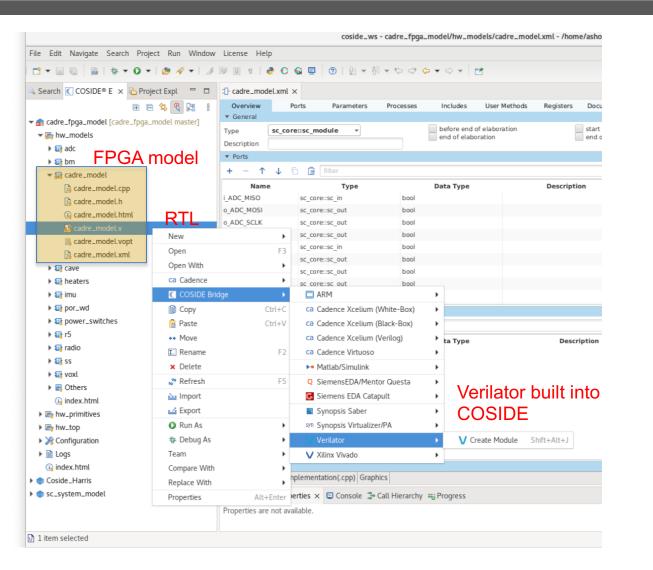

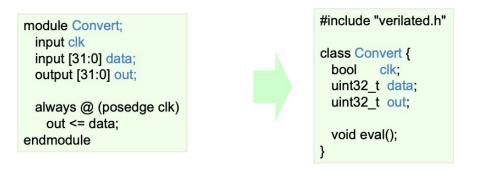

- 1. Add the synthesizable Verilog RTL to your COSIDE project

- 2. Right click the Verilog file and navigate to COSIDE Bridge > Verilator > Create Model

- 3. COSIDE module will be created

- 4. Create other components required in your testbench either by importing or coding

- COSIDE Generates SystemC code from RTL

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

#### Simulation

| File Edit Navigate Search Project Run Wind | ow License Help   |                   |             |              |              |      |          |       |       |      |

|--------------------------------------------|-------------------|-------------------|-------------|--------------|--------------|------|----------|-------|-------|------|

| 📑 🕶 🔚 🐚 🗟 💁 🕶 🛷 🕶 🧶 🖼 🖷                    | 0 🖗 👻 🐺 🕶 🌾       | • 🔶 🕶 🗢 🕞 🗣 🔎     | P A A X     |              | A 🗘 📖        |      |          |       |       |      |

| T-mod_A.xml T-mod_B.xml 🗄 tb_top.sca       | ml 🖻 pwc_src_sc.h | 🛃 mod_top.scaml 📫 | - mod_C.xml | ₩ *tb_top_sc | simctrl_tb.v | :d 🛙 |          |       |       |      |

| C.                                         | ò                 | 2.5               | -6          | 5e           | -6           |      | 7.5e-6   | 10e-6 |       | 12.5 |

| SystemC.i_tb_top.unnamedNet2               |                   | 0                 | X 10        | X 20 X       | 30           | 40   | X 50 X   |       | 60    |      |

| SystemC.i_tb_top.unnamedNet3               | - IC              | 0                 | X 100       | X 200 X      | 300          | 400  | X 500 X  |       | 600   |      |

| SystemC.i_tb_top.i_mod_top1.unnamedNet1    | - C               | 0                 | 222         | X 444 X      | 666          | 888  | X 1110 X |       | 1332  |      |

| SystemC.i_tb_top.i_mod_top1.unnamedNet2    |                   | 0                 | X 20        | X 40 X       | 60           | 80   | X 100 X  |       | 120   |      |

| SystemC.i_tb_top.s_mod_top_out             | -                 |                   |             |              |              |      |          |       |       |      |

| SystemC.i_tb_top.s_rst                     | -                 |                   |             |              |              |      |          |       |       |      |

| SystemC.i_tb_top.unnamedNet1               | - C               | 0                 | X 1         | X 2 X        | 3            | 4    | X 5 X    |       | 6     |      |

|                                            | 6                 | 2.56              | -6          | 5e           | 6            |      | 7.5e-6   | 10e-6 | · · · | 12.5 |

## Steps:

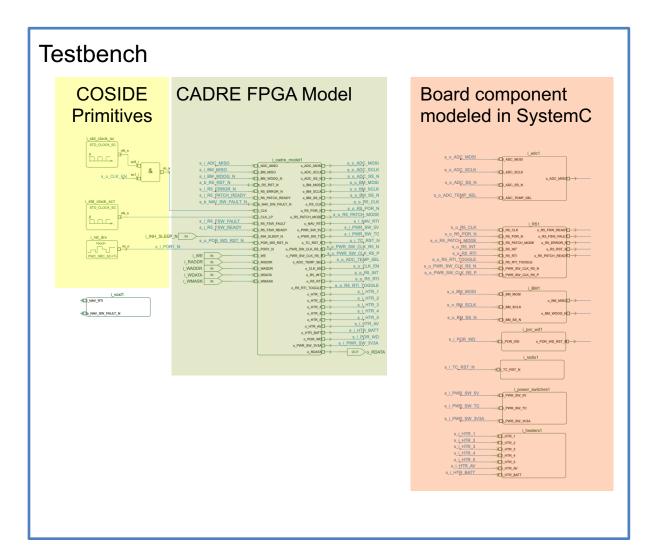

- 1. Create a TB with peripheral device models

- 2. Simulate to verify proper functionality

# Software Model (IPC method)

Jet Propulsion Laboratory California Institute of Technology

CADRE – Cooperative Autonomous Distributed Robotic Exploration

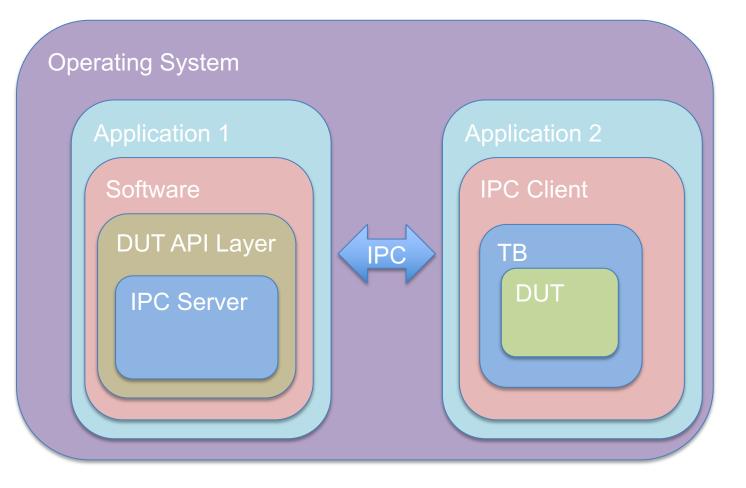

## Pros:

- 1. No library dependence for Application 2 since it's compiled on COSIDE.

- 2. Very easy to setup. COSIDE automatically finds all input/output ports in the TB

- Application 1 can be in any language. COSIDE provides IPC Server in Python and C++

# Cons:

- 1. COSIDE IPC only supports wiggling TB ports. (signal level communication)

- 2. Need to poll the DUT, can't create event triggers

- 3. Expect slowdown due to IPC overhead

- 4. API Layer falls on Software side

# Software Model (IPC method)

Jet Propulsion Laboratory California Institute of Technology

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

#### How To:

1. Setup SystemC Client

SC\_REPORT\_ERROR("top\_simple\_tb","Failed to attach to C-main master");

hdl.start();

}

# 2. Setup Server (Python shown, C++ is similar)

# 3. Run. Read all Registers

print("\nStart simulation...")

# create quick access handle

i\_RADDR\_s = hdl.get\_object\_handle("i\_RADDR\_s")

i\_WADDR\_s = hdl.get\_object\_handle("i\_WADDR\_s")

i\_WDATA\_s = hdl.get\_object\_handle("i\_WDATA\_s")

i\_WMASK\_s = hdl.get\_object\_handle("i\_WMASK\_s")

i\_INH\_SLEEP\_N\_s = hdl.get\_object\_handle("i\_INH\_SLEEP\_N\_s")

o\_RDATA\_s = hdl.get\_object\_handle("o\_RDATA\_s")

# write i\_INH\_SLEEP\_N using handle

hdl.write(i\_INH\_SLEEP\_N\_s, "0")

hdl.run(0.250) # run simulation for 250ms

print("Current time: %3.2e" %hdl.get\_time\_in\_seconds())

for i in range(20):

#read reg

hdl.write(i\_RADDR\_s, str(i))

hdl.run(10\*1e-6/32.0+1e-12); #run 10 clock cycles plus small delta

val = hdl.read(o\_RDATA\_s)

print("Read Address is {:x} Read Data is {:x}".format(i, int(val)))

hdl.run(1) #run for 1s

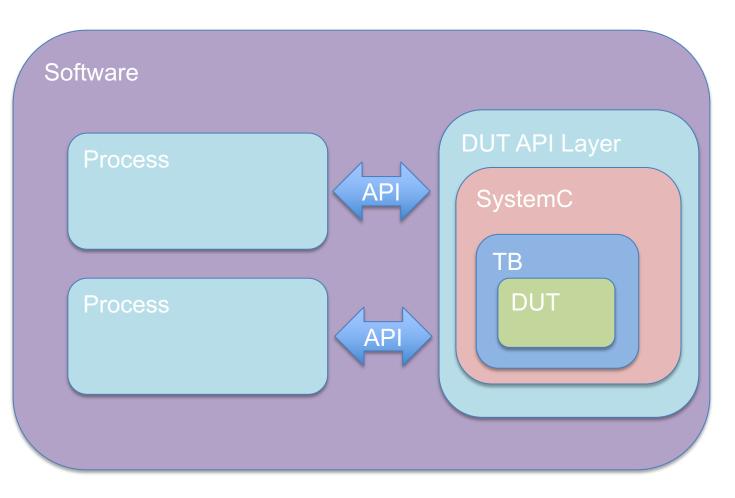

# Software Model (RAW SystemC)

Jet Propulsion Laboratory California Institute of Technology

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

#### Pros:

- 1. No IPC overhead

- 2. Software has access to source code

- 3. Can react to DUT events

- 4. More control over TB

## Cons:

- 1. Requires some trickery of SystemC Main

- 2. Software has to resolve SystemC and other hardware library dependencies

Performance: 1 sec sim = 1 min wall clock

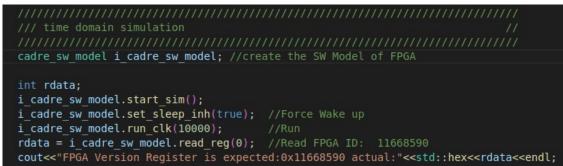

# Software Model (RAW SystemC)

Jet Propulsion Laboratory California Institute of Technology

**CADRE – Cooperative Autonomous Distributed Robotic Exploration**

## Read a register from the FPGA model

## Set the battery temperature in Battery Monitor model

```

// set BM return value

// Battery temperatures

// These are 12-bit DN values corresponding to specific battery temperatures.

// The values come from Bob's MathCad tool.

i_cadre_sw_model.i_components->i_BM1.ext_temp1 = BM_TEMP_POS30C;

// Read BM

cout<<"BM Temps"<<endl;

for (int i = 0x13; i < 0x15; i++)

{

rdata = i_cadre_sw_model.read_reg(i);

cout << "Register address:0x" << std::hex << i << " data:0x" << rdata << endl;

}

```

# **APIs:**

#### Read

```

int cadre_sw_model::read_reg(uint address){

i_CNAV_RADDR.write(address);

run_clk(10);

int rdata = o_CNAV_RDATA.read();

return rdata;

```

```

}

```

#### Write

```

void cadre_sw_model::write_reg(uint address, int data){

i_CNAV_WADDR.write(address);

i_CNAV_WMASK.write(0xffffffff);

i_CNAV_WDATA.write(data);

i_CNAV_WE.write(true);

run_clk(1);

i_CNAV_WE.write(false);

run_clk(50);

}

```

# Run Clock

```

void cadre_sw_model::run_clk(uint cycles){

double one_clk_period = 1e-6/32.0;

double sim_time = cycles * one_clk_period + 1e-12;

sc_core::sc_start(sim_time, sc_core::SC_SEC);

```

```

}

```